Рекомендации по проектированию аппаратуры

Данный документ содержит рекомендации по разработке принципиальной электрической схемы устройства на базе микросхемы СКИФ.

До начала разработки устройства рекомендуется тщательно ознакомиться с настоящим документом.

Основным документом по микросхеме СКИФ является руководство пользователя.

Питание микросхемы

- Если для управления питанием доменов используется источник питания, поддерживающий управление сигналом EN, то выводы OFFREQ/OFFACK необходимо �подключать к EN/PGOOD.

- Если питание доменов CPU, SDR, MEDIA статично или управляется через другой интерфейс, то соответствующие выводы OFFREQ/OFFACK необходимо подключать друг к другу.

- Если режим работы с отключением домена CORE не поддерживается, вывод CORE_OFFREQN можно не подключать.

- Питание на КП можно подавать одновременно с включением домена CORE, независимо от его уровня (3.3 В или 1.8 В), так как по сбросу КП настроены в режим 3.3 В. Время нарастания уровня питаний не менее 15 мкс.

- Для 3.3 В дополнительных настроек уровня не требуется.

- Для 1.8 В нужно изменить настройку в регистрах, и через время ~2 мкс начать полноценную работу.

- Все напряжения питания домена BAT (BVDD, BAT_VDDO, BAT_VDDPST)

должны сохраняться:

- BVDD обеспечивает питание домена,

- BAT_VDDO питает КП XTI32K_XIN/OUT,

- BAT_VDDPST питает КП CORE_OFFREQN и NRST_PON.

- Уровень сигнала NRST_PON должен соответствовать уровню BAT_VDDO.

- Домен BAT включает ядро таймера реального времени RTC, контактные площадки CORE_OFFREQ, XTI32K и NRST_PON.

- Питание домена BAT:

- BVDD = 0.9 B.

- BAT_VDDPST = 1.8 B.

- BAT_VDDO = 1.8 B.

- Питание нужно подавать с погрешностью 5%.

- Объединять с �питанием ядра обязательно, даже если домен BAT не используется:

- BVDD с CVDD,

- BAT_VDDPST с COREVDDPST,

- BAT_VDDO с COREVDDPST.

Фильтрация напряжений

- Конденсаторы должны быть размещены на нижней стороне платы, под корпусом микросхемы, максимально близко к переходным отверстиям, которые, в свою очередь, подключены напрямую к опорным слоям земли и питания. Расстояние между конденсаторами и переходными отверстиями - не более 1,27 мм.

- Использовать конденсаторы с максимальной ёмкостью для выбранного типоразмера.

- Возможна установка дополнительных конденсаторов большой ёмкости на верхней стороне печатной платы, по периметру корпуса микросхемы.

- Конденсаторы следует устанавливать как можно ближе к выводам микросхемы.

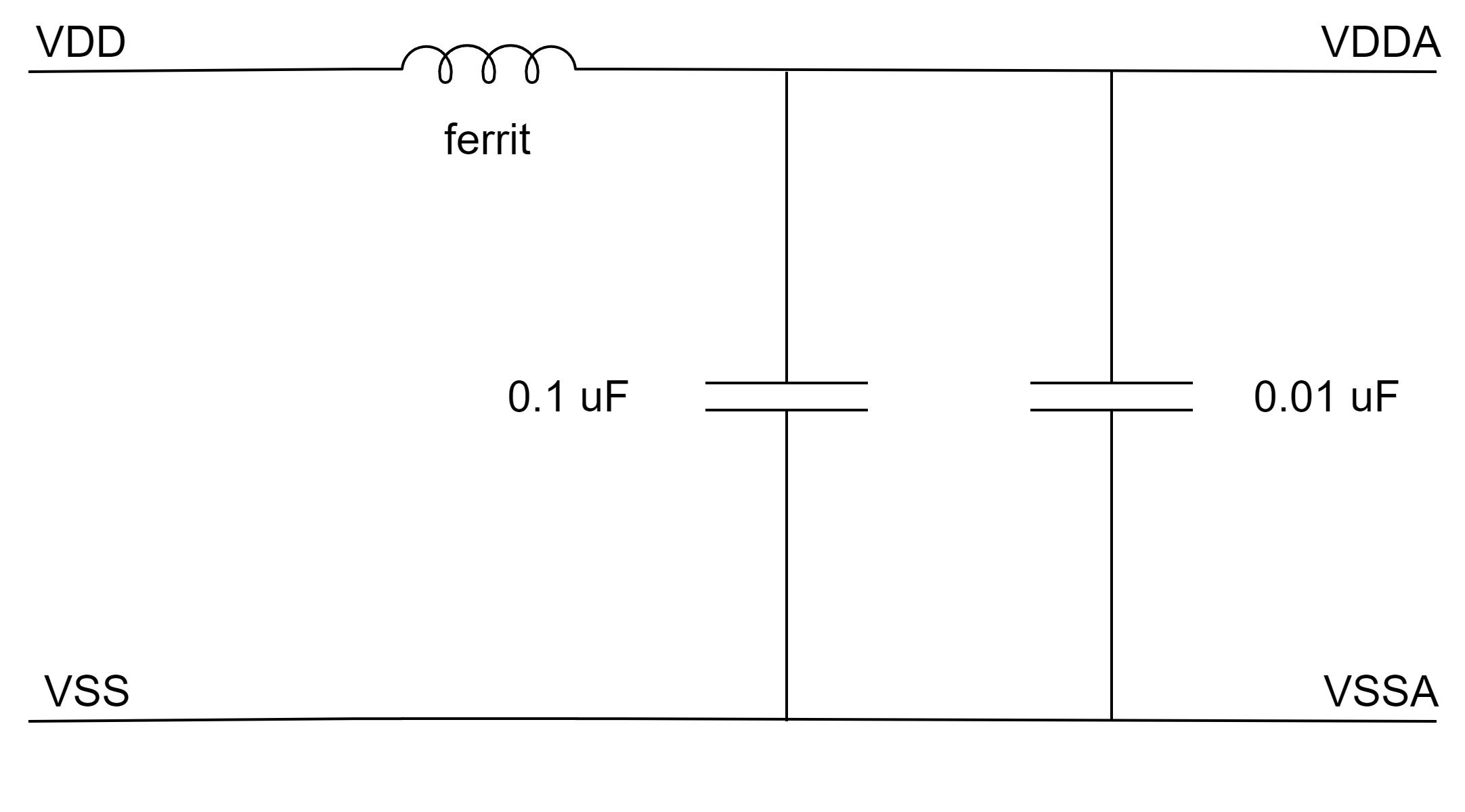

Питание PLL

- Входы питания PLL должны быть отфильтрованы с помощью LC фильтр�а и двух шунтирующих конденсаторов емкостью не менее 0,1 мкФ и 0,01 мкФ.

- Основные характеристики, которые стоит учесть при выборе феррита:

- Сопротивление постоянному току около 0,4 Ом.

- Импеданс на частоте 10 МГц равен или больше 180 Ом.

- Импеданс на частоте 100 МГц равен или превышает 600 Ом.

- Рекомендованные фильтры: BLM18EG601SN1 или BLM15AX601SN1.

Типы и количество конденсаторов (пример для модуля ELV-MC03-SMARC)

| Выводы м/с (название цепи на схеме) | Тип конденсатора (мкФ) | Количество |

|---|---|---|

| DDR0_VDDQ, DDR1_VDDQ | 4.7 | 3 |

| 1 | 25 | |

| DDR0_VREF, DDR1_VREF | 0.1 | 3 |

| 4.7 | 1 | |

| DDR0_VAA, DDR1_VAA | 0.1 | 1 |

| eMMC_VDDIM | 0.1 | 1 |

| 1 | 1 | |

| VDDPST | 4.7 | 5 |

| HSP_VDDO_SDMMC0 | 0.47 | 4 |

| HSP_VDDO_SDMMC1 | 0.47 | 1 |

| HSP_VDDO_EMAC | 0.47 | 4 |

| HSP_VDDO_MISC | 0.47 | 2 |

| HSP_VDDO_PLL | 0.47 | 1 |

| MVDD | 0.47 | 50 |

| SVDD | 0.47 | 76 |

| CVDD | 0.47 | 47 |

| AVDD | 0.47 | 21 |

Тактовые частоты микросхемы, резонаторы и генераторы

-

Технические характеристики генераторов и резонаторов представлены в таблицах 52.2-54.4 руководства пользователя на процессор СКИФ. Подключение резонатора 32 КГц выполнять в соответствии c 52.4 Подключение резонатора 32 КГц РП.

-

Частота кварца XTAL может быть 27 МГц (в РП СКИФ указывается 27.456 МГц). Посадочное место кварца должно быть совместимо с кварцем или программируемым генератором на 27.456 МГц.

-

Частота 27.456 МГц является основной рабочей, т.к. на ней удобнее реализовывать SDR, но не является обязательной.

Схема подключения генератора 27МГц для модуля ELV-MC03-SMARC -

Вместо кварца 32.768 кГц рекомендуется использование генератора.

-

Резонатор 32.768 kHz. Соединить выводы резонатора с выводами XTI_32K и XTO_32K. Выбрать резонатор с эквивалентным сопротивлениям не более 100 Ом и следовать рекомендациям производителя по ёмкостной нагрузке.

-

Конденсаторы (обычно 10-16 пФ) необходимы для уменьшения паразитных емкостей. Дорожки между резонатором и процессором должны быть короткими, необходимо наличие плоскости заземления под кристаллом, конденсаторов нагрузки.

-

Для стабильной работы LPDDR4 рекомендуется выбирать кварцы со стабильностью не ниже 20 ppm.

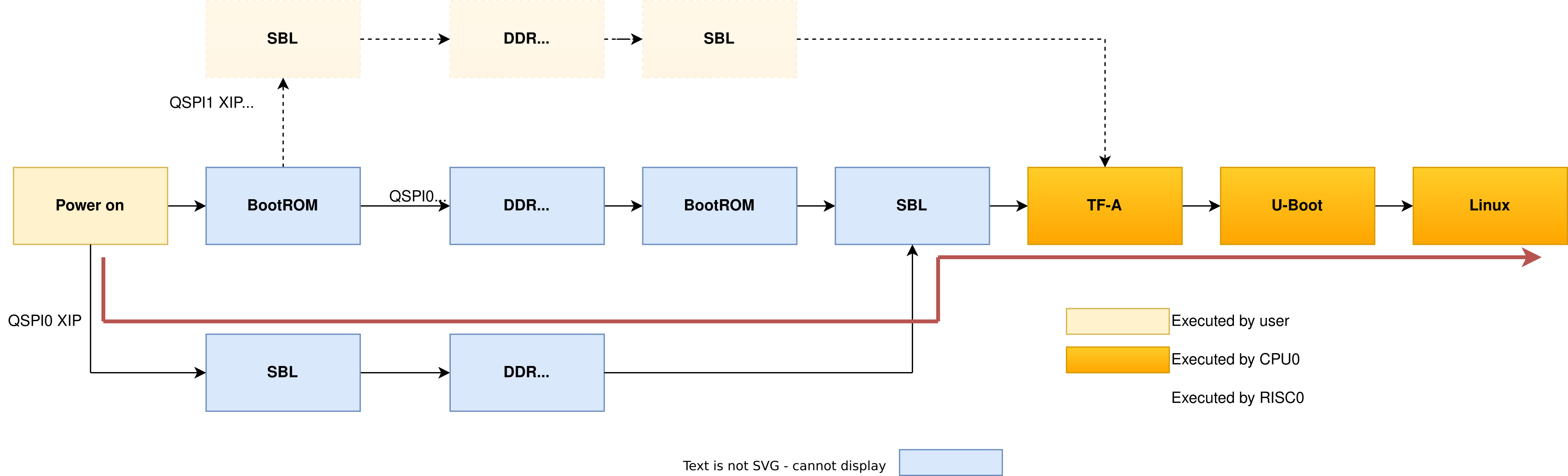

Режимы загрузки микросхемы

- В зависимости от требований по безопасности (уровня сертификации) и ПО обеспечивающего безопасность для каждого устройства разрабатываются индивидуальные требования к аппаратной платформе.

- Требования по минимальной безопасной загрузке с проверкой подписей:

- Загрузка должна выполняться средствами BootROM с одного из носителей: QSPI0, MFBSP0 SPI, eMMC 1.8 В, SDMMC0.

- Примечание: QSPI0, MFBSP SPI доступны только из доверенного контура. eMMC 1.8 В, SDMMC0 доступны из недоверенной операционной системы.

- Пины Boot должны быть установлены в соответствующий режим загрузки, либо режим загрузки должен быть задан конфигурацией OTP.

- При выборе размера ОЗУ необходимо учитывать, что 256 МБ будет использовано доверенным контуром.

Таблица: Режимы загрузки

| Режим | Описание | Возможности Настройки КП, В | Настройки КП BootROM, В | Безопасная загрузка |

|---|---|---|---|---|

| b000 | QSPI0 XIP | 1.8 | N/A | ❌ |

| b001 | BootROM RISC0/QSPI0 | 1.8 | 1.8 | ✅ |

| b010 | BootROM RISC0/MFBSP0 SPI | 1.8 | 1.8 | ✅ |

| b011 | BootROM RISC0/UART0 | 3.3 | 3.3 | ❌ |

| b100 | BootROM RISC0/eMMC 1.8В | 3.3 | 1.8 | ✅ |

| b101 | BootROM RISC0/QSPI XIP CPU0 | 1.8/3.3 (при сбросе) | 1.8 | ❌ |

| b110 | BootROM RISC0/SDMMC0 3.3В | 3.3 | 3.3 | ✅ |

| b111 | noBoot (RISC0 ожидает сеанс отладки) | N/A | N/A | ❌ |

b100: Только eMMC. Режим не работает из-за ошибки в BootROM.

b101: Не рекомендуется использовать, т.к. ARM CPU не может настраивать PLL интерконнектов.

В режимах загрузки ROM/QSPI0, ROM/MFBSP0 SPI, ROM/QSPI1, необходимо учитывать:

- Если используется память размером более 16 МБ, то необходимо

выполнять одно из условий:

- Необходимо обеспечить сброс питания памяти по низкому уровню сигнала MFBSP0.LDAT4 процессора.

- Необходимо гарантировать, что высокоуровненое ПО не переведёт микросхему памяти в 4-байтовый режим адресации.

- Если используется память размером 16 МБ и менее, то сброса памяти не требуется.

- Перед обращением к флеш-памяти BootROM выполняет сброс низким уровнем на выводе MFBSP0.LDAT4. BootROM работает с флеш-памятью в 3-байтовом режиме адресации. В случае если ПО перевело флеш-память в режим 4-байтовой адресации (применимо к флеш-памятям размером более 16 МБ), то для перевода в 3-байтовый режим требуется сброс флеш-памяти.

В режиме загрузки QSPI0 XIP необходимо учитывать:

- Если используется память размером более 16 МБ, то ПО управляющее флеш-памятью на QSPI0 не должно переводить флеш-память в 4-байтовый режим адресации.

- Официально поддерживаются:

- W25Q

- MX25L

- S25FL

- N25Q

- По умолчанию контроллер QSPI0 использует команду 0x03 (однобитное чтение) с 3-байтовым адресом, которую поддерживает большинство SPI-памятей объёмом не более 16 МБ.

- КП блоков QSPI0 и MFBSP могут работать только на 1.8 В.

- КП блока QSPI1 толерантны и к 1.8 В и к 3.3 В, причем по сбросу настроены на работу от 3.3 В

- Технология памятей QSPI0, QSPI1, MFBSP SPI должна быть NOR (NAND не поддерживается).

- Сброс NRSTWRM должен происходить после того, как источники питания вышли на оптимальный режим работы. Для этого можно использовать POWERGOOD от источников питания или другие способы задержки (например RC-цепь).

Сигналы сброса микросхемы

NRST_PON

Подключить через 12 кОм резистор к цепи питания 1.8 В. Сброс по включению питания - приводит к переводу в начальное состояние всей логики микросхемы без исключения.

NRST_WRM

Сигнал «теплого» сброса микросхемы. «Теплый» сброс – аналогичен сбросу по включению питания, однако не приводит в начальное состояние трассы и таймеры реального времени. Логика отладки частично приводится в начальное состояние.

Отладочные порты

Для задания режима отладки подать на входы TESTMODE, JMODE0, JMODE1 значение согласно требуемому интерфейсу (См. Таблица 51.13. Перечень сигнальных выводов. Служебные выводы).

- При TESTMODE = 0;

- 0x0 - RISC0 JTAG;

- 0x1 - USOC USB0;

- 0x2 - USOC JTAG;

- 0x3 - зарезервировано.

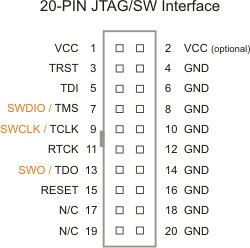

Подключение JTAG

Необходимы внешние подтягивающие резисторы на сигналах JTAG (TDI, TMS, TCK, TRSTN - pull up, TESTMODE pull down).

| Вывод | Назначение | Подтягивающие резисторы |

|---|---|---|

| TMS | Выбор режима теста | 100 кОм - VCC |

| TDO | Выход данных теста | — |

| RTCK | Тестовый тактовый сигнал | — |

| TDI | Вход данных теста | 100 кОм - VCC |

| TRSTN | Установка исходного состояния | 100 кОм - VCC (не обязательный) |

| TCK | Test ClocK pin | 100 кОм - VCC |

| RESET | Вывод RESET | 100 кОм - VCC |

Подключение UltraSoC

Для работы UltraSoC требуется подавать 125 МГц на вывод CLK125. После включения питания источник частоты не должен требовать программирования.

SERV_SPARE1 (SCAN_EN)

На исследовательских платах должен быть установлен переключатель 1.8 В / GND для включения режима DFT.

В конечных устройствах вход должен быть подтянут к GND.

Подключение внешних устройств

Проверена работа с сенсорами OmniVision OV4689, OV2718, OV5647 по интерфейсу MIPI CSI.

Рекомендации, не привязанные к интерфейсам

В зависимости от параметров платы могут оказаться необходимыми схемотехнические решения для согласования цепей. Необходимость таких решений определяет разработчик аппаратуры самостоятельно

Организация интерфейсов

DDR

- Допускается произвольное свапирование битов (DQ) внутри байта. Свапирование байтов не поддерживается.

- На исследовательской плате MCom-03-BuB на вход DDR0/1_VREF подается напряжение 1.1 В.

- Поддерживаемые конфигурации контроллеров: DDRMC0 и DDRMC1.

Display Port

Частота PIXCLK формируется только при высоком уровне сигнала DE. Полноценного обхода проблемы нет. В качестве временного - на изготовленных платах можно использовать вместо PIXCLK сигнал CMOS0_CLK блока CSI. Однако, такой вариант не позволяет добиться надёжной работы, т.к. этот сигнал не синхронизирован с данными VPOUT. Проконтролировать эту ситуацию программными средствами возможности нет.

Не рекомендуется использовать параллельный порт с HDMI-трансиверами. Необходимо использовать DSI-HDMI или DSI-DP трансиверы, либо использовать трансмиттер с собственным источником тактового сигнала.

Ethernet

EMAC

Рекомендуется использовать разъёмы с гальванической развязкой (HFJ11-1G41E-L12RL). В случае, если используется разъём без гальваноразвязки, необходимо трансформаторами обеспечить независимость сигнальной цепи (АО НПЦ "ЭЛВИС" такое решение не использовалось).

Микросхемы PHY

Список микросхем PHY, с которыми проверялась работа:

- DP83867IRRGZR

- KSZ9031RNXIC

GPIO

- Прерывания только на порте A.

- Если используется SPI0, то вывод GPIO0_PORTC_3 должен использоваться только для функций SPI0. Аналогично с выводом GPIO1_PORTC_7 для SPI1. Подробнее см. SPI0, SPI1.

- Если используется расширитель GPIO с поддержкой прерываний, то для обеспечения корректной обработки прерываний следует выбирать расширитель с наличием регистров-защелок. Например PCAL9555A от NXP.

ISP parallel

- Сигналы параллельного порта являются двунаправленными и могут быть использованы как для ввода, так и для вывода видео. По умолчанию порт работает как вход.

- Специальных требований к разводке сигналов параллельного порта нет.

- Если порт не используется, вход клока PIXCLK должен быть подключен к земле, остальные сигналы могут быть оставлены неподключенными.

- Для подачи частоты на CMOS сенсор могут быть использованы выводы CMOS0/1_CLK, для сброса CMOS сенсора - выводы GPIO.

ISP MIPI CSI

- Для подключения входов данных и клока (MIPI_RX0/1_DATAP0...DATAP3, MIPI_RX0/1_DATAN0...DATAN3 и MIPI_RX0/1_CLKP/CLKN) рекомендуется использовать разъемы с импедансом 50 Ом и полосой пропускания > 3 ГГц.

- В цепях питания MEDIA_MIPI_RX0/1_VP(0.9В) и MEDIA_MIPI_RX0/1_VPH(1.8 В) рекомендуется устанавливать развязывающие конденсаторы ёмкостью 0,47мк.

- Для дифференциальных пар рекомендуется поддерживать дифференциальное сопротивление 100 Ом на частоте 1250 МГц, разводить их в верхнем слое без переходных отверстий. Сигналы в дифференциальной паре должны разводиться симметрично с максимальным перекосом 10 ps.

- Если все выводы питания MIPI DPHY (аналоговые и цифровое) подключены, неиспользуемые выводы данных, клока и REXT могут быть либо подключены к земле, либо оставлены висящими. Если аналоговое питание VPH висит неподключенным, выводы данных, клока и REXT должны быть либо подключены к земле. Остальные выводы питания не рекомендуется оставлять неподключенными.

- Выходы CMOS0/1_CLK могут быть использованы для подключения референсных клоков для CMOS сенсоров. Для некоторых сенсоров т�ребуются сигналы кадровой синхронизации (например, входы TRIG у некоторых сенсоров Aptina), для этой цели предназначены СMOS0/1_FSYNC (синхронизируются клоками CMOS0/1_CLK). Если сенсор не требует кадровой синхронизации, эти выходы можно оставить неподключенными.

- Опционально: к пину MIPI_RX0_REXT рекомендуется подключать резистор на землю номиналом 200 Ом 1%.

- На сигналы VTEST0-7 выводится информация о внутреннем состоянии ISP. Если возникнут проблемы с подключением нового сенсора на новой плате, информация о состоянии ISP может быть полезна.

I2C

- К контроллеру I2C4, который относится к сервисной подсистеме, не рекомендуется подключать ничего, кроме устройств, обеспечивающих безопасность, например, контроллера питания микросхемы СКИФ или контроллера управления размыкателями устройств.

- Линии I2C должны иметь внешнюю подтяжку к высокому уровню. Номинал резисторов выбирается в зависимости от конкретной платы и зависит от ёмкости линии. По спецификации время нарастания сигнала на линиях I2C не должно превышать 300 нс для режима Fast-mode (400 кГц) и 1000 нс для режима Standard-mode (100 кГц). Обычно подтягивающие резисторы имеют номинал 2.2 кОм для работы в режиме Fast-mode. Встроенные в пады подтягивающие резисторы имеют слишком большой номинал и не смогут обеспечить работу на скорости Fast-mode.

I2S

В процессоре есть аппаратная ошибка. Контроллер может работать только в режиме master.

NFC/NAND

Требования к корректировке в ECC памяти (количество корректируемых ошибок/размер блока в байтах) не должны превышать возможности коррекции ECC в СКИФ.

- 1/512

- 2/512

- 4/512

- 8/512

- 12/512

- 16/512

- 24/512

- 1/1024

- 2/1024

- 4/1024

- 8/1024

- 12/1024

- 16/1024

- 24/1024

Подключение 8-бит 2-die, 16-бит 2-die, 2-х 8-битных памятей и 8-бит 2-die с независимой шиной данных выполнять в соответствии с 52.6 NAND Руководства пользователя.

PCIe

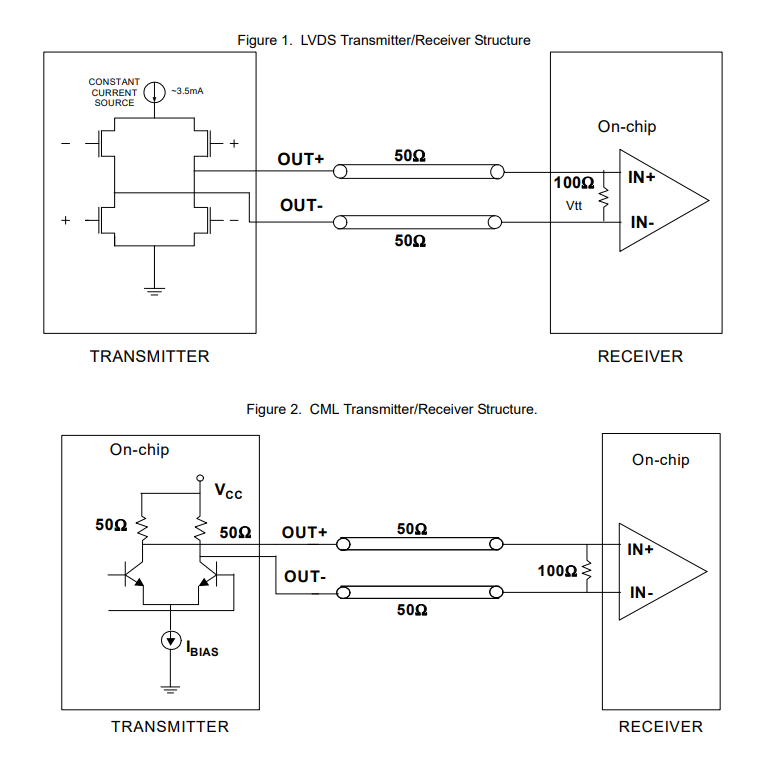

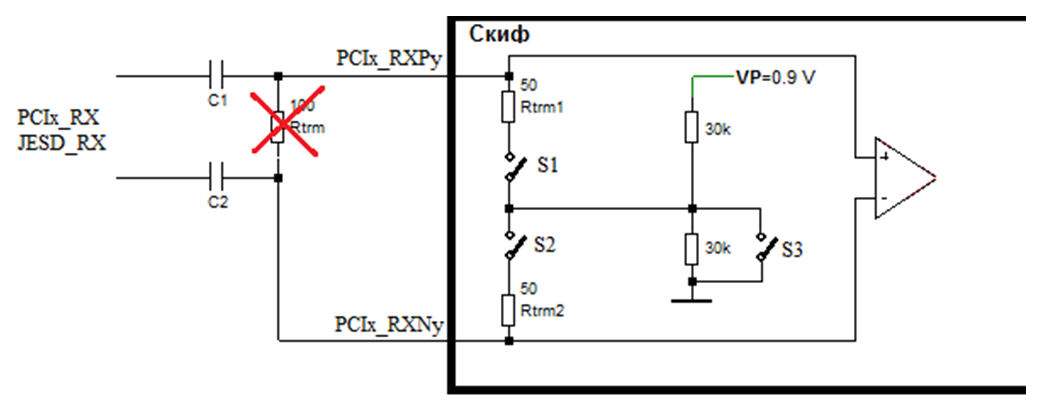

- Для PCIe на исследовательской плате MCom-03 BuB используется развязка по переменному току, так как на плате физически интерфейс JESD выведен на PCI. На физическом уровне JESD использует токопереключающую логику CML.

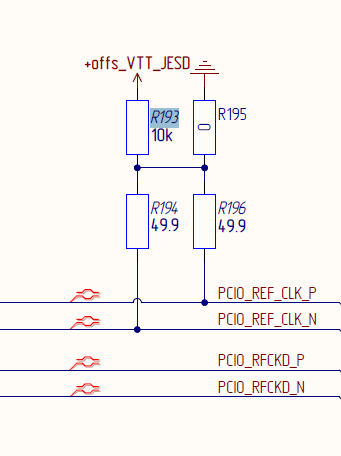

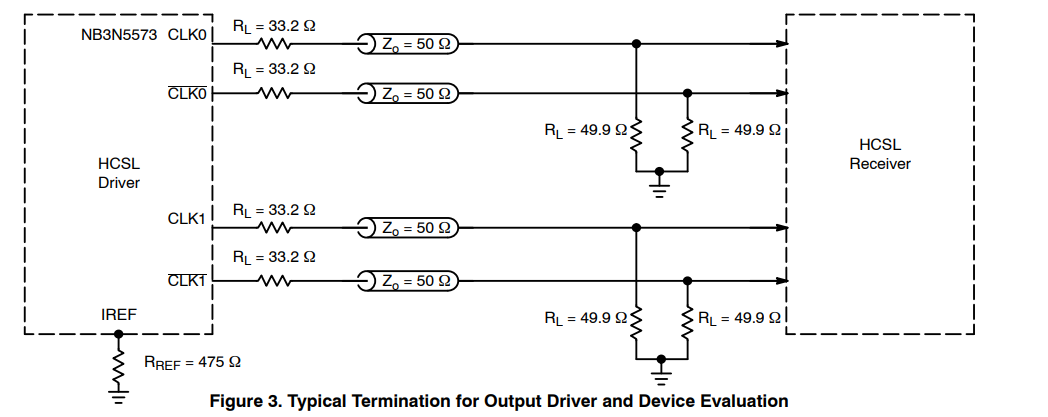

- Тактирование контроллера PCIx_REF_CLKx производится генератором импульсов HCSL частотой 100МГц. Схемы терминации определяются документацией на данный HCSL генератор.

- Для выводов SDR_PCIE0/1_VPH допускаются значения напряжений в диапазоне 1.5 – 1.8 В.

- Уровни сигналов PCI*_PERSTN, PCI*_WAKE, PCI*_CLKREQ-1.8 В.

- CLKREQ и WAKE работают в режиме Open-drain, что позволяет на плате подтянуть их при необходимости к 3.3 В.

- Пины A14 B14, E14, D14 — это входы референсной частоты для PCIe:

- A14 - PCI0_REF_CLK_M

- B14 - PCI0_REF_CLK_P

- E14 - PCI1_REF_CLK_M

- D14 - PCI1_REF_CLK_P

Частота PCIx_REF_CLK должна быть равна 100 МГц, тип выводов HCSL. 25 МГц на исследовательской плате – это ошибка. Внутренних терминирующих элементов (резисторов, конденсаторов) на входах референсной частоты для PCI нет, рекомендуется ставить внешние конденсаторы, указанные в таблице:

| Протокол | Мин. | Макс. | Единицы |

|---|---|---|---|

| PCIe 1.1 and PCIe 2.1 | 75 | 200 | нФ |

| PCIe 3.0 | 180 | 265 | нФ |

Для PCIe используется развязка по переменному току. На физическом уровне JESD использует токопереключающую логику CML. Соединение CML и LVDS приёмников и передатчиков приводится на рисунке ниже. Из этого можно сделать вывод, что следует использовать схему терминирования из даташита на микросхему: https://www.onsemi.com/pdf/datasheet/nb3n5573-d.pdf

Через резисторы R193 и R223 10k на исследовательской плате MCom-03 BuB обеспечивается необходимое смещение для дифференциальных сигналов. Из этого же смещения определялся номинал этих резисторов 10k.

Опорная тактовая частота PCIx_REF_CLK формируется на модуле и подаётся на процессор, за пределы модуля не выходит. Тактирование контроллера PCIx_REF_CLKx производится источником HCSL клока частотой 100МГц. Все согласующие сопротивления определяются микросхемой, формирующей эту частоту и длинами трасс.

Root Complex

- Сигнал PCI_WAKE разъёма не подключать к процессору. Выход PCI_WAKE микросхемы оставить неподключенным.

- Соединить сигнал PERSTn микросхемы через подтягивающий резистор 10 кОм с "землей".

- Сделать pull-down сигнала PERSTn c чипа к земле.

- Сброс Endpoint-устройства (сигнал PERST#) должен подаваться с GPIO процессора.

- Напряжение PERST# 0/3.3 В. Для GPIO 1.8 В нужен внешний преобразователь уровней.

- Заземлять CLKREQ#, если его нет на разъёме (т.е. Conventional PCIe). Во всех остальных случаях подтягивать его к 3.3 В.

- Не рекомендуется использовать обратный порядок лейнов PCIe: в этом случае нельзя будет в софте установить режим x1.

Endpoint

- Брать REFCLK(+/-) со слота, а не с генератора на плате.

- WAKE#, CLKREQ#, PERST# подключать со слота на SoC через преобразователь 3.3 В - 1.8 В.

- Для CLKREQ# сделать DNP-подтяжку вниз (на случай, если функциональность CLKREQ# не заработает).

- Для WAKE# сделать DNP-подтяжку вверх (на случай, если WAKE# подаёт в процессе инициализации spurious interrupt).

PCI_RX

Для SOC СКИФ необязательно иметь внешние терминирующие резисторы 100 Ом по дифференциальным входам PCI1_RX и PCI0_RX. Внутри микросхемы есть возможность программного включения встроенных терминирующих резисторов. Управление включением этих резисторов будет доступно через драйвер интерфейса JESD_PCI, в исходном коде которого значения битовых полей можно будет изменять. Включение и отключение встроенных резисторов зависят от значения битовых полей драйвера: EN, TERM_ACDC, TERM_EN.

Табли�ца: Значения битовых полей

| EN | TERM_ACDC (Включает S3) | TERM_EN (Включает S1 и S2) | Входное сопротивление дифф.входа, Ом |

|---|---|---|---|

| 0 | X | X | 100 |

| 1 | 0 | 0 | — |

| 1 | 0 | 1 | 100 |

| 1 | 1 | 0 | — |

| 1 | 1 | 1 | 100 |

На схеме внутреннего терминирования ключи S1 и S2 одновременно включаются битом TERM_EN. Состояние S3 зависит от бита TERMh_ACDC. В случае если бит EN установлен в 0 (либо после сброса процессора) ключи S1, S2, S3 находятся в замкнутом состоянии. При использовании сигнала с гальванической развязкой конденсаторами, предпочтительное значение конфигурации бит соответствует строке 3 из таблицы значений битовых полей (внутреннее терминирование и внутренняя подтяжка к уровню 0.45 В). Для выводов PCIх_RX допустимые значения напряжений должны быть в диапазоне 0 – 0.9 В (в случае использования источника дифференциального сигнала без гальванической развязки).

QSPI

- Для QSPI0 - IO всегда 1.8 В (в домене COREVDDPST).

- Для QSPI1 - при использовании для загрузки, рекомендуется использовать HSP_VDDO_QSPI напряжение 3.3 В, так как после ресета все регистры настроены на режим 3.3 В.

- Для обоих каналов на микросхему памяти заводится системный ресет.

- Для обоих каналов памяти рекомендуется ставить на CS подтяжку 1 кОм из-за проблем с фронтами режима IO после ресета.

- QSPI0 доступен с RISC0, QSPI1 доступен с RISC0 и CPU0.

- См. также раздел Режимы загрузки микросхемы.

SDMMC/eMMC/SDIO

SD

- Пример подключения SD-контроллера к SD-карте с переключаемым напряжением питания 1.8 В/3.3 В см. Рисунок 9.11. HSPERIPH. Особенности интеграции SDMMC0 (режим SD) в руководстве пользователя.

- В м/с СКИФ присутствуют подтяжки к "1" на WP, CDN. WP=1 - включена защита от записи. CDN=0 - карта установлена.

- При загрузке с SD средствами BootROM необходима внешняя подтяжка к единице на линии CMD. На других линиях внешняя подтяжка не требуется.

eMMC

Загрузка с eMMC средствами BootROM невозможна.

SDIO

Внешних подтяжек на линиях CLK, DAT, CMD не требуется.

Служебные сигналы

WP - активный уровень высокий. L: запись разрешена; H: запись запрещена.

nCD - активный уровень низкий. L: карта установлена; H: карта отсутствует.

SPI0, SPI1

- Для работы шины SPI, контактная площадка сигнала SPIx_SS_IN должна быть в аппаратной функции.

- Если к SPI0, SPI1 подключен ведомый работающий по протоколам Motorolla SPI, National MicroWire, то SPIx_SS_IN должен быть подтянут к 1.

- Если к SPI0, SPI1 подключен ведомый работающий по протоколу Texas Instruments SSP, то SPIx_SS_IN должен быть подтянут к 0.

- Если сигнал SPIx_SS_IN не выводится на контактную площадку, по умолчанию он подтянут к нулю, шина SPI может работать только по протоколу Texas Instruments SSP.

- При наличии на шине SPI одного мастера, к контактной площадке

сигнала SPIx_SS_IN подключение специальной логике:

- Не требуется:

- Если не требуется использовать динамическую смену последовательного протокола;

- Либо при динамической смене протокола не используется протокол Texas Instruments SSP;

- Требуется:

- Если используется динамическая смена последовательного протокола. И один из этих протоколов будет Texas Instruments SSP.

- Не требуется:

- При наличии на шине SPI несколько мастеров сигнал SS_N[0] одного мастера заводится на пин SPIx_SS_IN другого мастера.

UART

При использовании RISC0 необходимо выводить UART0

- При использовании терминала ОС (Linux) на CPU0 требуется выводить UART1 (UART0 недоступен с CPU0 при включенной безопасности).

- Питание переходников UART-USB должно подаваться от кабеля USB. В противном случае, при подаче питания на переходник с модуля, устройство /dev/ttyUSBx на ПК изменяет имя при каждом сбросе питания модуля

- BootROM включает подтяжку к земле на входе UART0_SIN номиналом 30...50 кОм. Из-за этого возникает просадка напряжения при использовании внешних микросхем согласования уровней с автоматическим определением направления (UM3204, TXS0102 и т.д.). Т.к. у них для формирования высокого уровня используется резистор, в результате возникает резистивный делитель. Для согласования уровней напряжения рекомендуется использовать однонаправленные push-pull преобразова�тели, например, SN74AXCH1T45.

USB

Согласование линий тактирования для USB выполняется по схеме.

Подключение неиспользуемых интерфейсов

Все неиспользуемые выводы типа «I», «IO» необходимо подключить к «земле», если не указано иное требование, или подтяжка этих выводов не обеспечивается самой микросхемой.

Подробнее см в Главе 51 РП на микросхему СКИФ.

Тестовые выводы в функциональном режиме работы микросхемы необходимо установить в значения, приведенные руководстве пользователя на микросхему СКИФ.

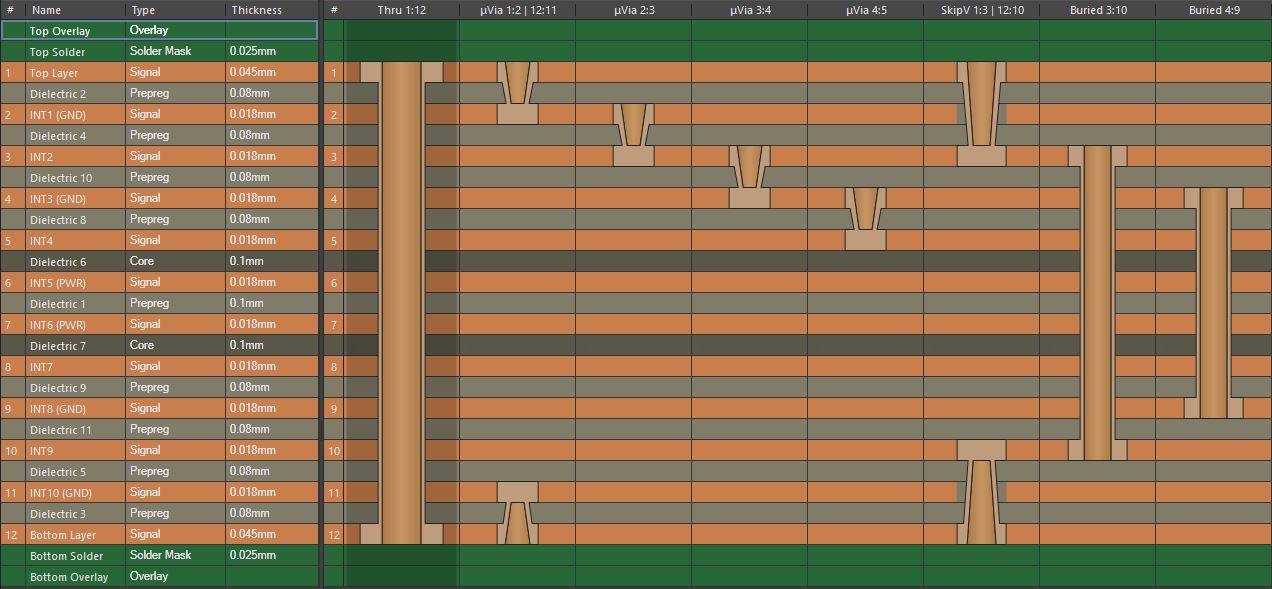

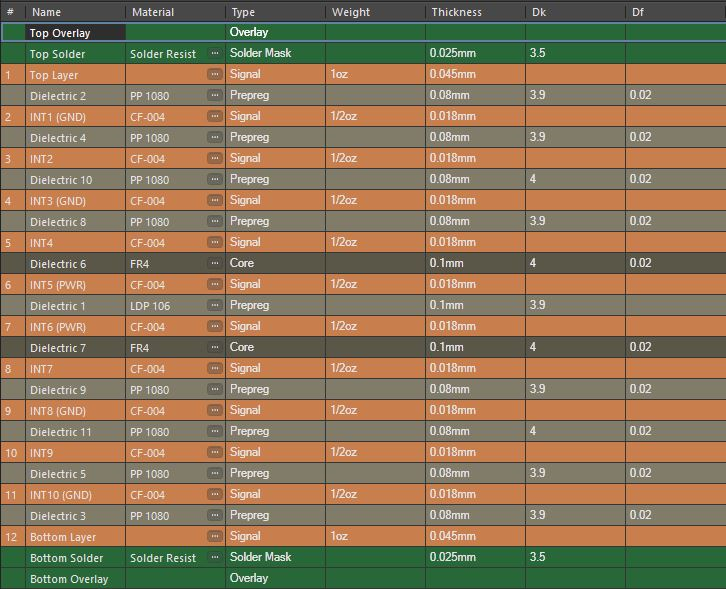

Рекомендации по топологии печатных плат

- ThroughVia 0.4/0.8 mm 0.2/0.4 mm 0.15/0.35 mm

- MicroVia 0.1/0.25 mm

- SkipVia 0.1/0.25 mm

- BuriedVia 0.15/0.3 mm