Рекомендации по проектированию аппаратуры

Введение

Данный документ содержит рекомендации и перечень необходимых проверок для разработчика принципиальной электрической схемы устройства на базе микросхемы 1892ВМ14Я.

Разработчику до начала разработки устройства рекомендуется тщательно ознакомиться с настоящим документом.

Функционал микросхемы 1892ВМ14Я описан в руководстве пользователя.

Настоящий документ представляет собой выдержку из руководства пользователя, акцентированную на вопросах проектирования принципиальной электрической схемы и приобретенный опыт инженеров АО НПЦ «ЭЛВИС».

Также рекомендуется ознакомиться с перечнем ограничений микросхемы 1892ВМ14Я.

В документе «Микросхема интегральная 1892ВМ14Я. «Рекомендации по трассировке DDR3» приведены рекомендации по подключению памяти DDR к микросхеме 1892ВМ14Я, в части, касающейся реализации топологии печатной платы.

В разделах настоящего документа, посвященных топологии печатных плат, в качестве иллюстраций используется топология модуля отладочного Салют-ЭЛ24Д1 rev. 1.5 , см. документацию.

Перечень контрольных проверок

В таблицах контрольных проверок, приведенных ниже (Таблица 2.1 - Таблица 2.14), содержатся рекомендации по оптимальному проектированию аппаратуры для устройств на основе микросхемы 1892ВМ14Я. В столбцах «Примечание» некоторых таблиц содержится объяснение, по�чему разработчику нужно придерживаться именно этой рекомендации.

Предлагается ознакомиться с документом «Микросхема интегральная 1892ВМ14Я. Рекомендации по трассировке DDR3».

В главе 17.9.2 «Примеры подключения» РП приведены примеры подключения флеш-памяти.

Напряжения питания микросхемы

Таблица 2.1

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Обеспечить порядок подачи питающих напряжений в соответствии с РП на микросхему. Обратить внимание на ограничение DDRMC, см. главу 7 документа «Микросхема интегральная 1892ВМ14Я. Перечень выявленных ограничений». | Несоблюдение порядка подачи питания может привести к повышенному потреблению на время до инициализации DDR | |

| Напряжение питания ядра находится в диапазоне допустимых напряжений (1.045-1.155 В) | ||

| Обеспечить максимальный ток источника питания ядра не менее 3 А. | ||

| Требования к максимальной �пульсации напряжения. | Шум пульсации должен быть менее 5% среднего значения напряжения. | |

| efuse_VDDA. Напряжение прожига eFuse. Данный вывод необходимо привязать к земле. |

Рекомендации по фильтрации напряжений питания микросхемы

Таблица 2.2

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Конденсаторы должны быть размещены на нижней стороне платы, под корпусом микросхемы, максимально близко к переходным отверстиям. Которые, в свою очередь, подключены напрямую к опорным слоям земли и питания. Расстояние между конденсаторами и переходными отверстиями - не более 1,27 мм. | ||

| Использовать конденсаторы с максимальной ёмкостью для выбранного типоразмера. | ||

| Возможна установка дополнительных конденсаторов большой ёмкости на верхней стороне печатной платы, по периметру корпу�са микросхемы. |

Типы и количество конденсаторов (пример для модуля Салют-ЭЛ24ПМ1)

Таблица 2.3

| Выводы микросхемы (название цепи на схеме) | Тип конденсаторов | Количество, шт |

|---|---|---|

| VDD (+1V1) | ||

| 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 36 | |

| 0603-22 мкФ-6,3 В (GRM188R60J226MEA0D) | 4 | |

| VDDPST | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 24 |

| DDR0_VDDQ, DDR1_VDDQ | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 14 |

| DDR0_VREF, DDR1_VREF | 0402-0,1 мкФ-16В (GRM155R71C104KA88D) | 4 |

| CSI_VDDAC, DSI_VDDAC | ||

| 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 4 | |

| 0603-22 мкФ-6,3 В (GRM188R60J226MEA0D) | 1 | |

| SDMMC0_VDD, SDMMC1_VDD | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

| SW0_VDD11, SW1_VDD11 | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

| SW0_VDD25, SW1_VDD25 | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

| OTG_VDD25 | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 1 |

| OTG_VDD33 | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

| ALIVE_VDD | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

| ALIVE_VDDPST | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

| RTC_VDD | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 1 |

| RTC_VDDPST | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

| RTC_VDDAC | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 1 |

| CPLL_VDDAC, APLL_VDDAC, SPLL_VDDAC, DPLL_VDDAC, VPLL_VDDAC, UPLL_VDDAC | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 3 |

| SW1PLL_VDDAC, SW0PLL_VDDAC | 0201-0,22 мкФ-6,3 В (GRM033R60J224ME15D) | 2 |

Тактовые частоты микросхемы, резонаторы и генераторы

Технические характеристики генератора и резонаторов представлены в таблицах 34.2-34.4 руководства пользователя на процессор 1892ВМ14Я.

Таблица 2.4

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Резонатор 32.768 kHz. Соединить выводы резонатора с выводами XTI_32K и XTO_32K. Выбрать резонатор с эквивалентным сопротивлениям не более 100 Ом и следовать рекомендациям производителя по ёмкостной нагрузке. Не использовать смещающий резистор, так как схема смещения присутствует внутри микросхемы процессора. | Конденсаторы (обычно 10-16 пФ) необходимы для уменьшения паразитных емкостей. Дорожки между резонатором и процессором должны быть короткими, необходимо наличие плоскости заземления под кристаллом, конденсаторов нагрузки. | |

| Подключить ко входу XTI_24M генератор 24 МГц. | Эта частота является опорной для контроллера управления синхронизацией CMCTR. | |

| Если для формирования XTI_24M используется кварцевый резонатор, необходимо подключение резистора 1 МОм параллельно резонатору. | Использование кварцевого резонатора для формирования частоты XTI_24M не является рекомендуемым решением. |

Сигналы сброса микросхемы (NRST_PON, NRST_WARM)

Таблица 2.5

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Сигнал установки исходного состояния NRST_PON подключить через 12 кОм резистор к цепи п�итания 3,3В. | Cброс по включению питания – приводит к переводу в начальное состояние всей логики микросхемы без исключения. | |

| Сигнал «теплого» сброса микросхемы NRST_WARM. | «Теплый» сброс – аналогичен сбросу по включению питания, однако не приводит в начальное состояние трассы и таймеры реального времени. Логика отладки частично приводится в начальное состояние. В качестве рекомендации по подключению см. рисунок 2.13 руководства пользователя на процессор 1892ВМ14Я. |

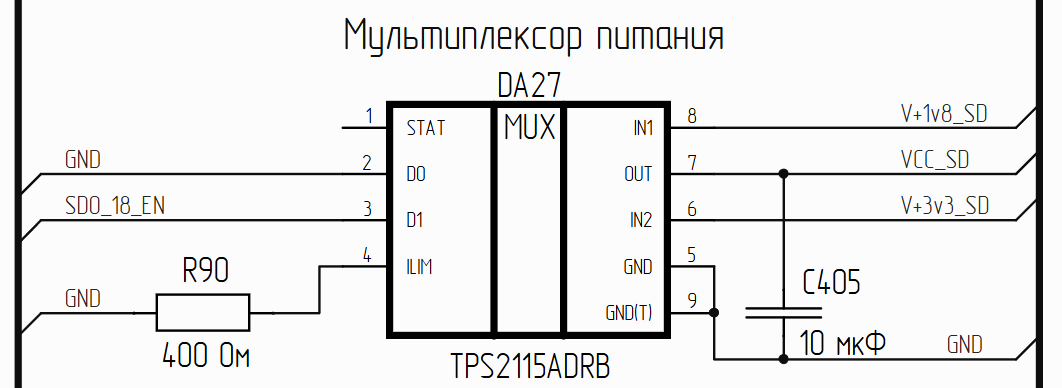

Рекомендации по подключению Питания SD карты

Стандарт SD предполагает возможность работы при напряжении питания 1,8 В и 3,3 В. Напряжение 1,8 В позволяет работать при более высокой скорости, см. Таблицу 20.54. «Максимальные значения частот для различных режимов работы SD» руководства пользователя. Таким образом, может потребоваться переключение на напряжение 1,8 В. Выбор питания определяется сигналами SDMMC0_18EN и SDMMC1_18EN.

Такое переключение используется в модуле отладочном Салют-ЭЛ24Д1 и представлена на рисунке ниже.

Для eMMC (подключаемых к тому же порту SDMMC) переключения питания не требуется.

Подтягивающие резисторы на линиях SDMMC

Рекомендуется подключать внешние pullup-резисторы 10...100 кОм на линии SD0_DET, SD1_DET.

Отладочные порты

Таблица 2.6. Рекомендации по JTAG

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Не применять внешние подтягивающие резисторы к цепи TDO. | Применение внешнего подтягивающего резистора может привести к некорректной работе. | |

| Система отладки TRACE не поддерживается программно. Соответствующие выводы могут быть �использованы в режиме GPIO. | ||

| На разъем JTAG должен быть выведен разъем NRST_PON. |

Таблица 2.7

| Вывод | Тип | Подтягивающий резистор внутри микросхемы | Подтягивающий резистор на схеме проектируемого устройсва |

|---|---|---|---|

| TDO | O | pullup, 10кОм | Нет необходимости |

| TCK | I | pulldown, 10кОм | |

| TRSTN | I | pullup, 10кОм | |

| TDI | I | pullup, 10кОм | |

| TMS | I | pullup, 10кОм |

Режимы загрузки микросхемы

Режим загрузки микросхемы задается состоянием выводов BOOT[2:0].

Таблица 2.8

| Проверено | Значение BOOT | Рекомендация | Примечание |

|---|---|---|---|

| BOOT = 0 | NOR Flash/EEPROM, необходимо подключать к NORMPORT. | ||

| BOOT = 1 | Только 8-ми разрядное подключение памяти. | Допустимые схемы подключения NAND-флэш приведены в разделе 17.9 руководства пользователя на микросхему 1892ВМ14Я Максимальная ёмкость под�ключаемой памяти NAND Flash - 128 Гбайт. Поддерживается как синхронный, так и асинхронный интерфейс. При загрузке с NAND-флеш корректировка ошибок с ECC не производится. При загрузке с SDMMC, SPI, NANDMPORT, UART (значение регистра BOOT не равно 0) происходит включение аппаратного механизма обеспечения когерентности, что может привести к зависанию процессора. Ограничение применимо к микросхемам партии: 1447,1544. | |

| BOOT = 2 | Порт UART0. | ||

| BOOT = 3 | SPI флэш необходимо подключать через блок SPI0 и CS0. | SPI FLASH доступна через порт SPI0. | |

| BOOT = 4 | SD-карту необходимо подключать к порту SDMMC0. | Код BootROM-sd осуществляет загрузку Secondary Program Loader (SPL) с SD/MMC карт. См. главу. 2 документа «Микросхема интегральная 1892ВМ14Я. Перечень выявленных ограничений. |

Не поддерживается загрузка со следующих типов носителей: eMMC в режиме MMC Boot mode; SDSC.

I2C

Таблица 2.9

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Проверить скорости подключаемых устройств. Не со�вмещать быстрые устройства с медленными. | Шина I2C работает на скорости самого медленного из подключенных устройств. | |

| Убедиться, что все подключаемые устройства на шине I2C имеют уникальные адреса. |

Ethernet

Таблица 2.10

| Проверено | Рекомендация | Примечание |

|---|---|---|

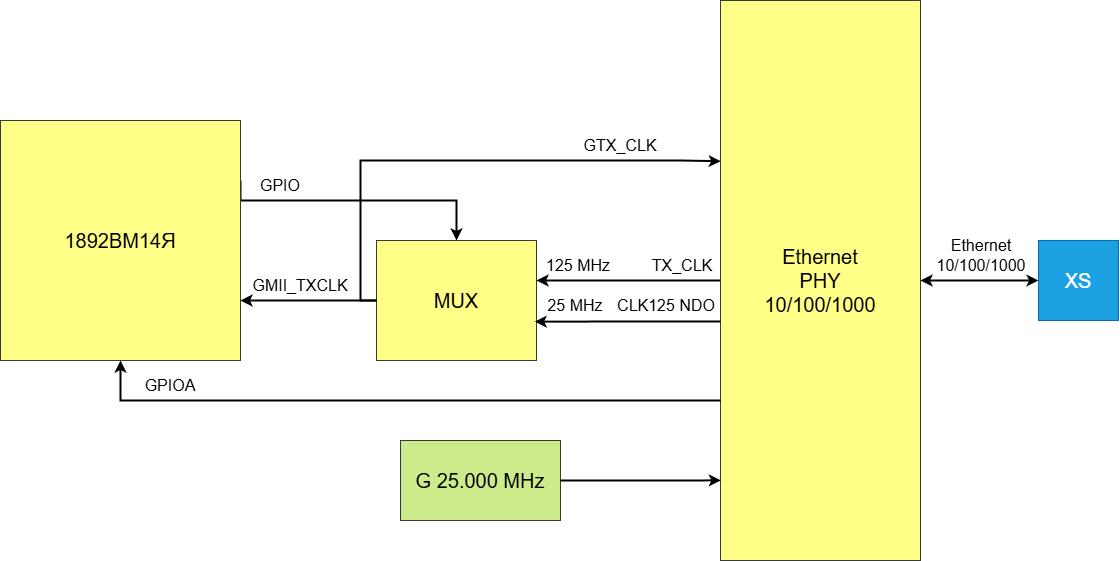

| Для переключения между режимами 1000 и 100 Мбит/с требуется внешний мультиплексор, см. рисунок 2.1. | Микросхема 1892ВМ14Я имеет только один тактирующий вход блока GEMAC – GMII_TXCLK. В случае, когда предполагается работать с сетями и на 100 Мбит/с, и на 1000 Мбит/с – необходима внешняя обвязка этого входа, позволяющая переключаться между источниками тактовой частоты. Ограничение применимо к микросхемам партии: 1447,1544. Решение: Использовать внешний мультиплексор, на вход которого подаются частоты 25 МГц и 125 МГц (для режимов 100 Мбит/с и 1000 Мбит/с соответственно), а выход которого подключен к выводу GMII_TXCLK микросхемы 1892ВМ14Я. В качестве источника частоты 125 МГц может использоваться внешний генератор. Управляющий вход мультиплексора должен управляться выводом GPIO микросхемы 1892ВМ14Я. Схема подключения представлена на Рисунок 2.2. Схема подключения внешнего мультиплексора. Процессор 1892ВМ14Я получает прерывание от микросхемы Ethernet PHY о факте подключения. Далее процессор читает регистры микросхемы Ethernet PHY и определяет максимальную доступную скорость в сети, и в зависимости от этого переключает мультиплексор. |

Микросхемы PHY

Список микросхем PHY, с которыми проверялась работа:

- KSZ9031MNXIA (100/1000 Mb/s) (Салют-ЭЛ24ПМ1).

- LAN8740A (100 Mb/s) (Салют-ЭЛ24Д1).

- DP83865 (10/100/1000 Mb/s) (плата ИП-КУ).

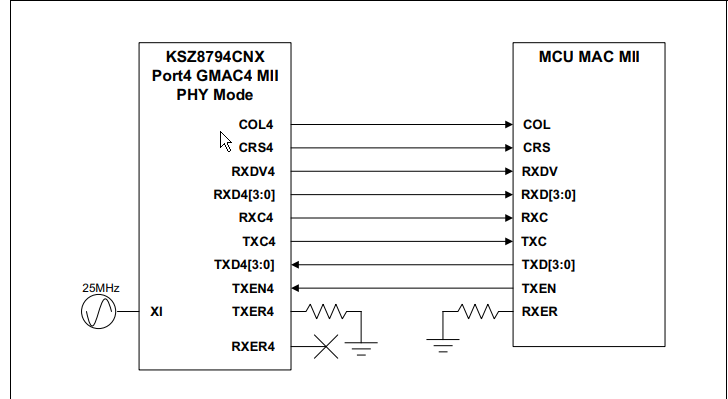

Производитель свитча может рекомендовать не подключать вывод RXER. Например как здесь:

В микросхеме 1892ВМ14Я вывод GMII_RXER имеет подтяжку к "1". В таком случае обязательно нужно подключать вывод GMII_RXER микросхемы к "0". Так как неподключение может привести в постоянному с�остоянию ошибки по приему на контроллере GEMAC.

Рекомендации по трассировке Ethernet-сигналов указаны в главе "Рекомендации по трассировке Ethernet".

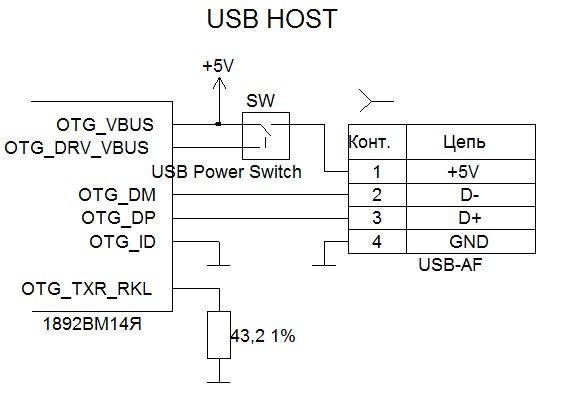

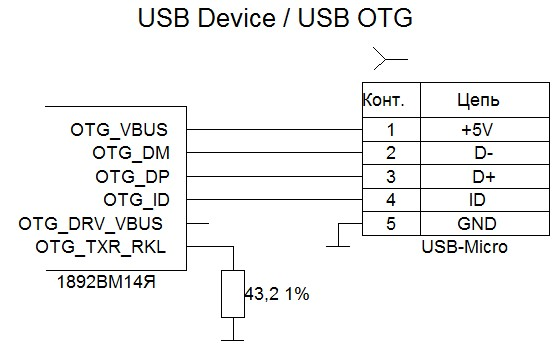

USB

Таблица 2.11

| Проверено | Рекомендация | Примечание |

|---|---|---|

| OTG_VDD33 входное аналоговое напряжение 3.3 В PHY порта USBIC. | ||

| OTG_VBUS напряжение (VBUS) работы/заряда USB от внешнего источника номиналом 5В. 0 5.25 В. | Данное напряжение должно быть подключено к выводу. | |

| OTG_TXR_RKL подключение калибровочного резистора (43.2 Ом±1%). | Резистор подключается с вывода на землю OTG_GNDAC. | |

| OTG_DRV_VBUS включение внешнего источника VBUS, данный вывод управляет внешним источником (схема заряда). | Данный вывод используется только в режиме Host: 0 – отключить регулятор питания VBUS; 1 – Включить регулятор питания VBUS. Если контроллер переведен в режим Device, то OTG_DRV_VBUS=0 | |

| OTG_VDD25 выходное аналоговое напряжение 2.5 В с внутреннего регулятора PHY порта USBIC. Вывод должен быть подк�лючен через конденсатор емкостью 0.1мкФ на OTG_GNDAС. | ||

| Использование электростатической защиты желательно для сигналов OTG_DP, OTG_DM. | ||

| OTG_ID. В режиме HOST должен быть подключен к GND напрямую. В режиме Device рекомендован внешний pull-up. |

Рекомендации по трассировке USB сигналов указаны в главе "Рекомендации по трассировке USB интерфейса".

Пример схемы подключения для режима HOST проиллюстрирован на рис. 2.3.

Примеры схемы подключения для режимов Device и Device с поддержкой On-The-Go проиллюстрированы на рис. 2.4. Режим Device с поддержкой On-The-Go отличается от режима Device наличием сигнала USB_OTG_ID на четвёртом контакте разъёма.

SWIC

Таблица 2.12

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Наличие внешних (fail-safe) pullup-резисторов номиналом 13 кОм у выводов SW0_DINN, SW0_SINN, SW1_DINN, SW1_SINN. | ||

| Наличие внешних (fail-safe) pulldown-резисторов номиналом 13 кОм у выводов SW0_DINP, SW0_SINP, SW1_DINP, SW1_SINP. |

DDR3

Таблица 2.13

| Проверено | Рекомендация | Примечание |

|---|---|---|

| Подключить DDRx_PZQ к GND через резистор 240 Ом 1%. | Опорный резистор используется в процессе калибровки выходных DRAM буферов. | |

| Подключить DDR_VREFx к напряжению, равному 50% от напряжения DDRx_VDDQ. | Возможно использование прецизионного резисторного делителя напряжения. При этом каждый резистор в делителе должен быть зашунтирован конденсатором 0,1 мкФ. При таком решении могут быть проблемы из-за дрейфа номиналов резисторов при изменениях температуры окружающей среды. Рекомендуется использование специализированных опорных стабилизаторов напряжения. Это решение дороже, зато повышает стабильнос�ть работы конечного устройства. | |

| Подключить DDRx_RESET к GND через резистор 10 кОм. | DDR3: DRAM_RESET необходимо удерживать в нуле, согласно стартовой JEDEC-последовательности, до тех пор пока контроллер памяти не будет сконфигурирован. | |

| Подключить DDRx_CKEy к GND через резистор 10 кОм. | Необходимо для минимизации токов утечки в спящем режиме. | |

| Необходимо для минимизации токов утечки в спящем режиме. | «1» - сброс внутренних счетчиков и схемы управления. Не влияет на значения полей управления. | |

| При трассировке использовать топологию симметричного T-дерева (T-Branch Topology). | Топология Flyby не поддерживается. | |

| Обеспечить программное управление источником питаний DDRx_VDDQ таким образом, чтобы после reset данное питание не подавалось на микросхему 1892ВМ14Я. | Если питание контактных площадок DDRx_VDDQ подается раньше, чем установлен в 0 разряд RET_DDRMCx в регистре DDR_PIN_RET, то возможно повышенное потребление по цепи DDRx_VDDQ до момента записи нуля в разряд RET_DDRMCx в регистре DDR_PIN_RET. Ограничение применимо к микросхемам партии: 1447, 1544. Решением является: обеспечение записи нуля в ра�зряд RET_DDRMCx регистра DDR_PIN_RET перед подачей питания контактных площадок DDRx_VDDQ. Это может быть сделано с помощью программного управления источником питания, формирующим напряжение DDRx_VDDQ. |

Рекомендации, не привязанные к интерфейсам

Таблица 2.14

| Проверено | Рекомендация | Примечание |

|---|---|---|

| В зависимости от параметров платы могут оказаться необходимыми схемотехнические решения для согласования цепей. Необходимость таких решений определяет разработчик аппаратуры самостоятельно |

Рекомендации по подключению неиспользуемых интерфейсов

Все неиспользуемые выводы типа «I», «IO» н�еобходимо подключить к «земле», если не указано иное требование, или подтяжка этих выводов не обеспечивается самой микросхемой.

Тестовые выводы в функциональном режиме работы микросхемы необходимо установить в значения, приведенные в таблице 33.14 руководства пользователя на микросхему 1892ВМ14Я.

Таблица 2.15

| Модуль | Выводы | Рекомендации по подключению в случае неиспользования |

|---|---|---|

| VPIN | ||

| GPIOC0- GPIOC31, VPIN_PIXCLKO, VPIN_PIXCLKO1, | Оставить неподключенными | |

| VPIN_FSYNC0, VPIN_FSYNC1, CSI0_DATAP0- CSI0_DATAP3, CSI0_DATAN0- CSI0_DATAN3, CSI0_CLKP, CSI0_CLKN | Подключить к «земле» | |

| VPOUT (MIPI DSI) | ||

| DSI_DATAP0, DSI_DATAP1, DSI_DATAP2, DSI_DATAN0, DSI_DATAN1, DSI_DATAN2, DSI_DATAN3, DSI_CLKP, DSI_CLKN | Подключить к «земле» | |

| VPOUT_VDO0- VPOUT_VDO23 | Оставить неподключенными | |

| VPOUT_VDEN, VPOUT_VSYNC, VPOUT_HSYNC, VPOUT_VCLK | Оставить неподключенными | |

| USBIC | ||

| OTG_DP, OTG_DM, OTG_TXR_RKL | Подключить к «земле» | |

| OTG_ID, OTG_VBUS, OTG_DRV_VBUS | Оставить неподключенными | |

| SWIC0, SWIC1 | ||

| SW0_DINP, SW0_DINN, SW0_SINP, SW0_SINN, SW1_DINP, SW1_DINN, SW1_SINP, SW1_SINN | Подключить к «земле» | |

| SW0_DOUTP, SW0_DOUTN, SW0_SOUTP, SW0_SOUTN, SW1_DOUTN, SW1_SOUTP, SW1_SOUTN, SW1_DOUTP | Оставить неподключенными | |

| MFBSP0, MFBSP1 | Для всех | Оставить неподключенными |

| EMAC | ||

| GMII_MDC, GMII_TXER, GMII_TXEN, GMII_TXD0 - GMII_TXD7 | Оставить неподключенными | |

| GMII_MD | Подключить к «земле» | |

| GMII_TXCLK, GMII_RXCLK, GMII_RXD0 - GMII_RXD7, GMII_COL, GMII_CRS, GMII_RXER, GMII_RXDV | Подключить к «питанию» |

В случае неиспользования таймера реального времени, кварцевый резонатор 32,768 кГц можно не устанавливать, тогда вывод XTI_32K необходимо подключить к "земле" или "питанию", а вывод XTO_32K – оставить неподключенным.

Рекомендации по топологии печатных плат

Данная глава содержит рекомендации по корректной трассировке печатных плат, спроектированных на базе процессора 1892ВМ14Я для силовых сигналов, интерфейсов.

В качестве примера используется модуль отладочный Салют-ЭЛ24Д1 ревизии 1.5.

Основные рекомендации

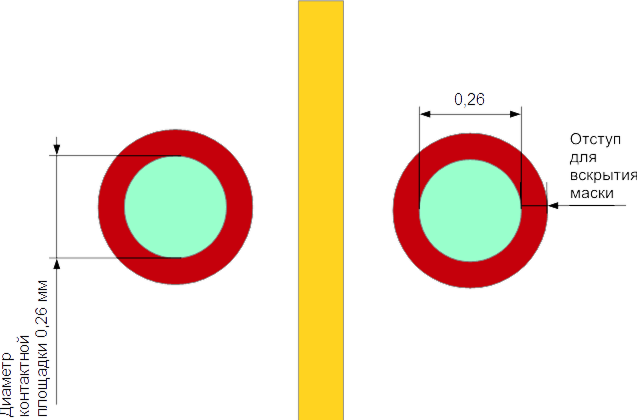

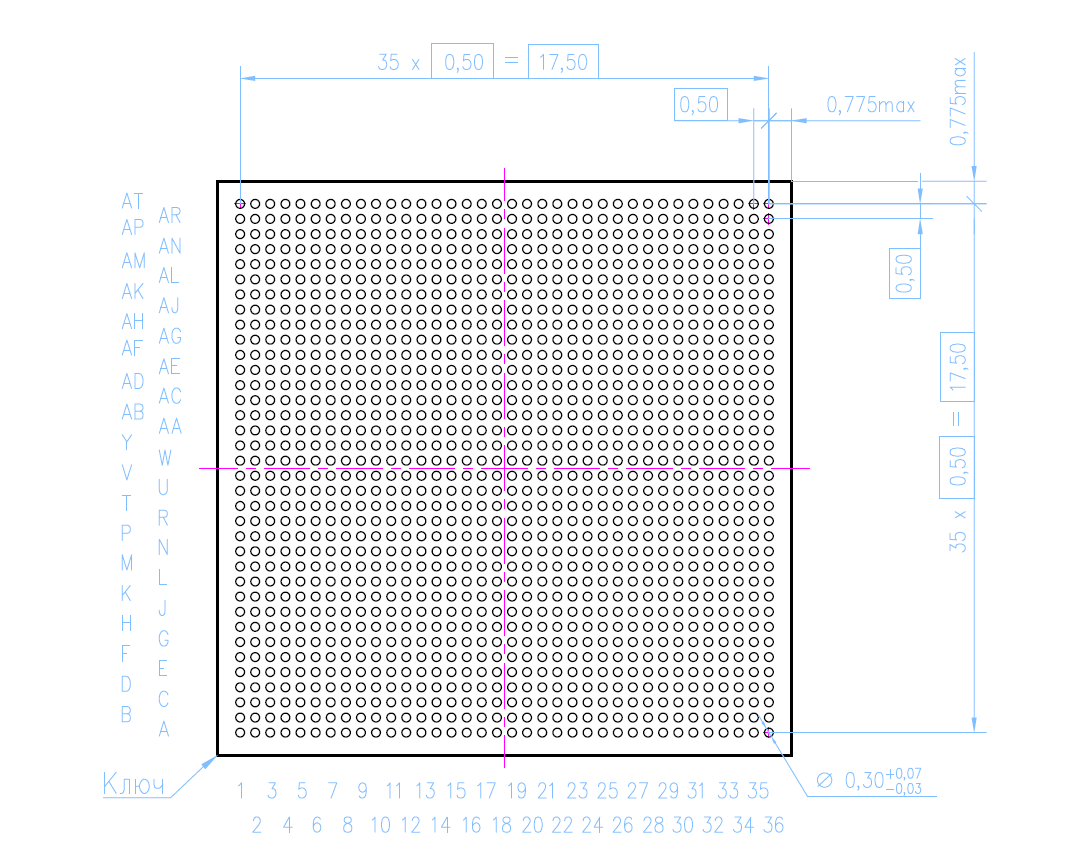

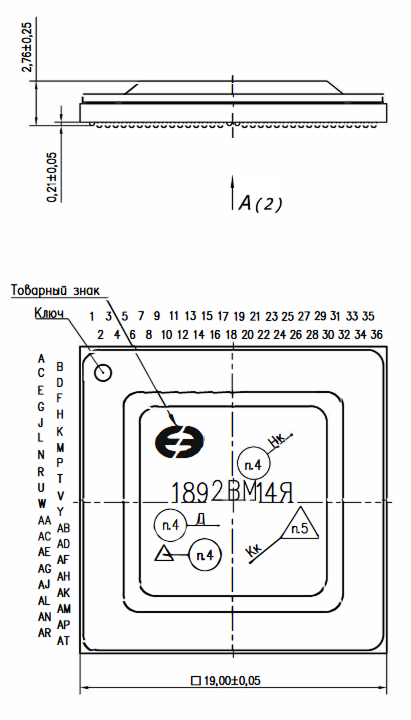

Микросхема 1892ВМ14Я изготавливается в корпусе HFCBGA-1296; размером 19x19 мм, шаг по выводам: 0,5 мм, матрица выводов: 36 x 36.

Диаметр контактной площадки 0,26 мм, Отступ для вскрытия маски 0,06 мм, не более, все зазоры не менее 0,076 мм, см. рис. 3.1, рис. 3.2.

Рисунок, представленный ниже, иллюстрирует матрицу выводов. Числовые данные о корпусе предоставлены на рис. 3.4.

Высокоскоростные интерфейсы

Рекомендуется разводить сначала высокоскоростные интерфейсы, затем низкоскоростные.

Высокоскоростные сигналы рекомендуется размещать в противоположных верхнем (top) и нижнем (bottom) слоях платы.

Низкоскоростные сигналы рекомендуется размещать во внутренних слоях платы, например, для 6-слойной платы в 3 и 4 слое.

Высокоскоростные дифференциальные пары сигналов (USB, Ethernet, SpaceWire) должны быть проложены с учетом дифференциального импеданса (между парой): необходимо придерживаться вычисленного значения.

Таблица 3.1. Рекомендации по дифференциальному импедансу высокоскоростных интерфейсов

| Интерфейс | Требуемый дифференциальный импеданс, Ом |

|---|---|

| USB | 90 |

| Ethernet | 95 |

| Space Wire | 100 |

Необходимо избегать изгибов, а если они требуется использовать тупой угол в 135° вместо прямого, см. рис. 3.5

Необходимо избегать T-образный цепей, так как они работают как антенны и могут усугублять проблем�ы, связанные с EMC (electromagnetic compatibility).

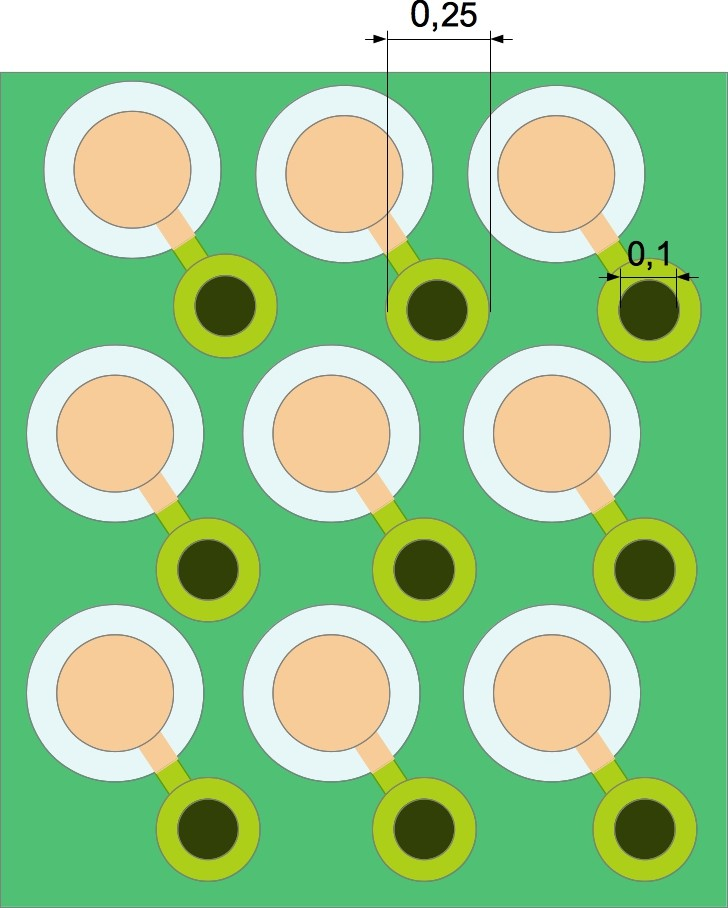

Размещение блокировочных конденсаторов

Блокировочные конденсаторы стоит размещать как можно ближе к переходным отверстиям цепей питания (power vias). Дополнительные блокировочные конденсаторы можно разместить по краю массива переходных отверстий (BGA via array). Размещение блокировочных конденсаторов вблизи от контактов питания критично, так как это позволяет минимизировать индукцию и обеспечить резерв энергии для пиковых потреблений цепи.

Цепи питания

По возможности, возле каждого вывода питания следует размещать блокировочный конденсатор. Если два вывода питания расположены близко друг к другу, допускается использовать для них один конденсатор. Следует укрупнять размер трасс питания и делать и�х как можно короче.

Рекомендации по трассировке DDR

Рекомендации по трассировке DDR изложены в отдельном документе «Микросхема интегральная 1892ВМ14Я. Рекомендации по трассировке DDR3» , доступном на сайте.

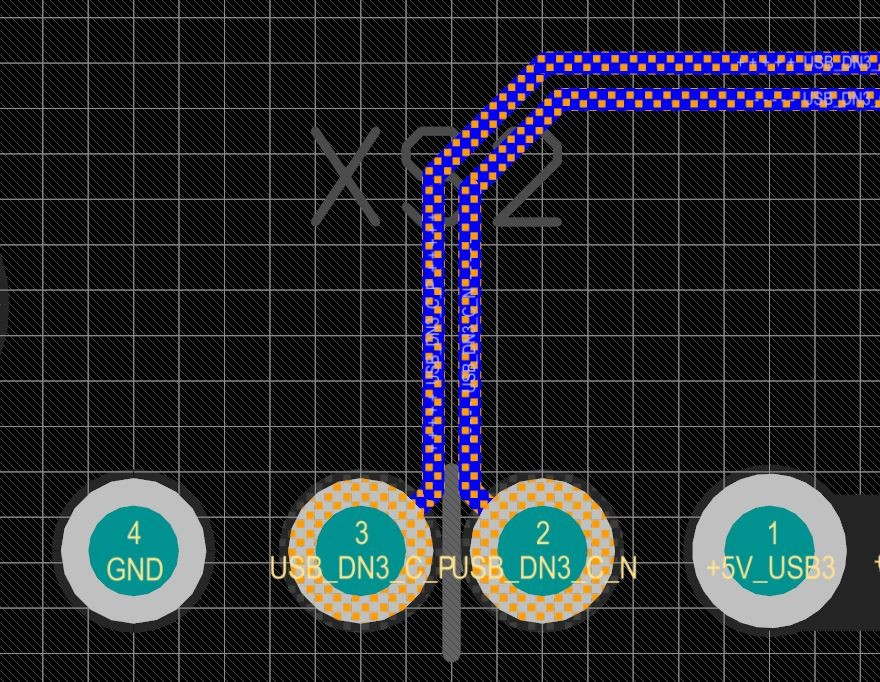

Рекомендации по трассировке USB интерфейса

- В первую очередь прокладывать сигналы дифференциальных пар OTG_DP и OTG_DN.

- Прокладывать сигналы дифференциальных пар OTG_DP и OTG_DN на слоях платы top либо bottom.

- Ширина трасс и расстояние между OTG_DP и OTG_DN должно быть таким, чтобы дифференциальное сопротивление было 90 Ом

- Трассы OTG_DP и OTG_DN должны быть одинаковой длины.

- Не проводить OTG_DP и OTG_DN трассы под осцилляторами или параллельно частотным трассам и шинам дан�ных.

- Минимизировать длину трасс OTG_DP и OTG_DN и количество углов (45 градусов вместо 90).

- Избегать смены слоев у OTG_DP и OTG_DN сигналов. Не создавать ветвлений.

Таблица 3.2

| Параметр | Требование |

|---|---|

| Дифференциальный импеданс | 90Ом ±15% |

| Опорный слой | GND или PWR (если PWR, то на обеих сторонах цепи необходимо установить конденсаторы между PWR и GND) |

| Максимальная разность в длине пары проводников | 1,1 мм |

| Максимальная длина трассы | 200 мм |

| Максимальное количество переходных отверстий | Минимально возможное |

Рекомендации по трассировке Ethernet

Таблица 3.3

| Параметр | Требование |

|---|---|

| Дифференциальный импеданс | 95Ом ±15% |

| Опорный слой | GND или PWR (если PWR, то на обеих сторонах цепи необходимо установить конденсаторы между PWR и GND) |

| Максимальная разность в длине пары проводников | 250 мкм |

| Максимальная разность в длине между парами проводников | 50 мм |

| Максимальная длина трассы | 100 мм, рекомендуется как можно короче |

| Минимальное расстояние между парами | 450 мкм |

| Минимальное расстояние между проводниками Ethernet и другими высокоскоростными сигналами | 7,5 мм |

| Минимальное расстояние между проводниками Ethernet и низкоскоростными сигналами | 2,5 мм |

| Максимальное количество переходных отверстий | 2 для всех проводников |

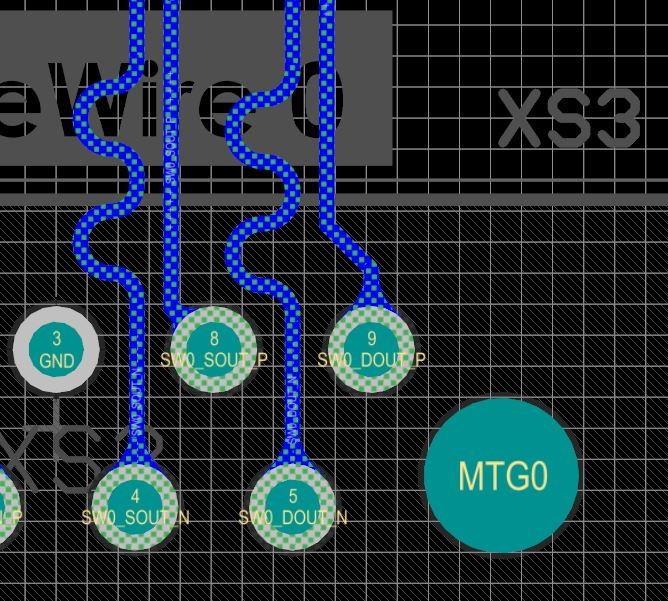

Рекомендации по трассировке SWIC

Применимы правила для дифференциальных пар.

SD/SDIO/MMC

Таблица 3.4

| Параметр | Требование |

|---|---|

| Дифференциальный импеданс | 50Ом ±15% |

| Опорный слой | GND или PWR (если PWR, то на обеих сторонах цепи необходимо установить конденсаторы между PWR и GND) |

| Максимальная длина трассы | 100 мм |

I2C

Таблица 3.5

| Параметр | Требование |

|---|---|

| Дифференциальный импеданс | 50Ом ±15% |

| Опорный слой | GND или PWR |

| Максимальная длина трассы | 450 мм |

MIPI/DSI

Таблица 3.6

| Параметр | Требование |

|---|---|

| Дифференциальный импеданс | 90 Ом ±15% |

| Опорный слой | GND или PWR (если PWR, то на обеих сторонах цепи необходимо установить конденсаторы между PWR и GND) |

| Максимальная разность в длине пары проводников | 150 мкм |

| Максимальная длина трассы | 200 мм |

| Максимальная разность в длине проводника сигнала данных и сигнала синхронизации | 1,5 мм |

| Максимальное количество переходных отверстий | Минимизировать |

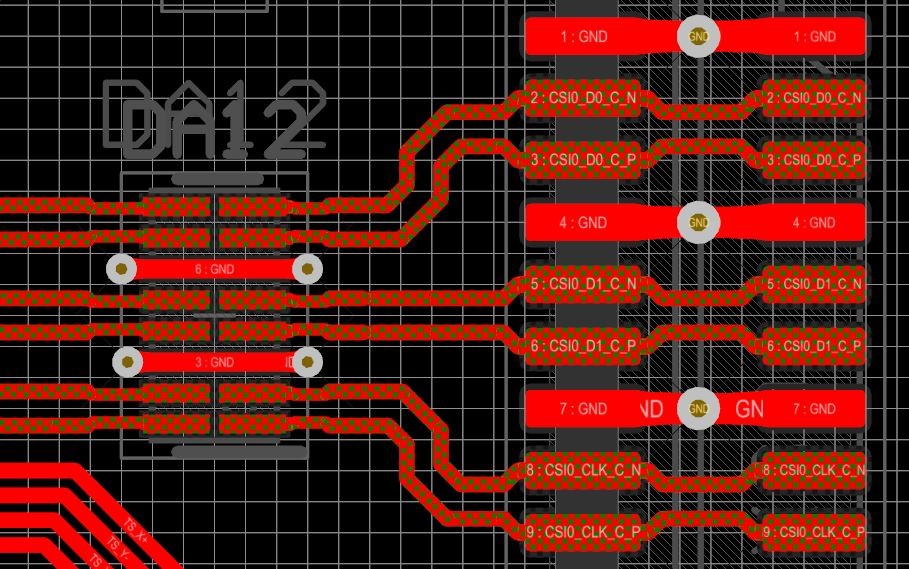

CSI

Таблица 3.7

| Параметр | Требование |

|---|---|

| Дифференциальный импеданс | 90 Ом ±15% |

| Опорный слой | GND или PWR (если PWR, то на обеих сторонах цепи необходимо установить конденсаторы между PWR и GND) |

| Максимальная разность в длине пары проводников | 150 мкм |

| Максимальная длина трассы | 200 мм |

| Максимальная разность в длине проводника сигнала данных и сигнала синхронизации | 1,5 мм |

| Максимальное количество переходных отверстий | Минимизировать |

Опорные резисторы

Рекомендуется размещать вдали от зашумленных областей. Индуцированный ими шум может повлиять на внутренние цепи и вредить интерфейсным сигналам.

Минимизация задержек и проблем расфазировки в дифференциальных парах

Дорожки сигналов дифференциальных пар должны быть разведены параллельно, симметрично, одинаковой длины. Для выравнивания длины использовать меандры, обращать внимание на выравнивание длины внутреннего проводника на поворотах. Не допускается размещение компонентов или переходных отверстий между дифференциальными парами.

Необходимо сократить до минимума количество переходных отверстий на трассах дифференциальных пар, размещать переходные отверстия симметрично.

Чтобы соблюсти требования по импедансу, обе трассы должны проходить в одних слоях с одинаковым количеством переходных отверстий.

Избегать разводки дифференциальных пар по краям печатной платы.

Некоторые из вышеупомянутых рекомендаций изображены на рис. 3.6, рис. 3.7.

Иногда требуется поместить на трассах дифференциальных пар разделяющие конденсаторы. Располагать их следует с�имметрично, размер предпочтительно выбирать 0402, 0603 является приемлемым, конденсаторы большего размера (0805) не использовать.

Аналоговая часть схемы

Аналоговую часть схемы стоит размещать на удалении от частотных цепей и источников питания. Разделять аналоговую и цифровую землю.

Рекомендации по подключению SPI флеш

При подключении SPI-флеш необходимо учитывать, что BootROM использует SPI-команды с 3-байтовой адресацией. Таким образом, необходимо убедиться в том, что используемая флеш поддерживает 3-байтный режим адресации в момент начальной загрузки, в противно�м случае такая память работать не будет.

IBIS-модель

Данная глава поясняет использование IBIS (input output buffer information specification) модели. Модель сгенерирована в текстовом ASCII формате и состоит из множества таблиц, отображающих зависимости тока от напряжения и напряжения от времени для каждого буфера. IBIS-модели используются для симуляции сигналов на уровне PCB и для временного анализа. Основополагающей идеей IBIS является моделирование работы интегральной схемы, не включающей подробности этого процесса.

Структура и содержимое

IBIS-файл содержит данные в ASCII-формате, требующиеся для поведенческого моделирования выводов и I/O буферов. Чаще всего, IBIS-файл состоит из следующих частей:

- Заголовок – содержит информацию о файле.

- �Информация о компоненте, электрических характеристиках корпуса, pin-to-buffer модель (какие выводы с какими буферами соединены).

Информация, содержащаяся в заголовке

Этот раздел IBIS-файла дает представление о файле и его данных. В таблице, приведенной ниже, расшифровываются строки заголовка.

Таблица 5.1

| Ключевое слово | Обязательно ли наличие этой строки в файле (да/нет) | Описание |

|---|---|---|

| [IBIS Ver] | да | Версия спецификации IBIS |

| [File Name] | да | Имя файла. Все имена должны быть написаны строчными буквами. Расширение для IBIS-файлов - .ibs |

| [File Rev] | да | Номер ревизии файла |

| [Date] | нет | Дата создания файла |

| [Source] | нет | Источник данных файла. Данные берутся из симуляции и валидации платы. |

| [Notes] | нет | Заметки и файле или компоненте. |

| [Disclaimer] | нет | Отказ от ответственности (дискламация) |

| [Copyright] | нет | Запись о копирайте. |

Ниже заголовок IBIS файла для микросхемы 1892ВМ14Я:

|************************************************************************

| IBIS file created by T2B Version 12.1.2.07111

| Cadence Design Systems, Inc. 2011

|************************************************************************

[IBIS ver] 5.1

[File name] mcom02_v2_1.ibs

[File Rev] 1.0

[Date] October 14, 2014

[Source] Synopsys, Inc. using Star-RCXT Z-2007.06-SP1 and

Star-HSPICE C-2009.09-SP1

[Notes]

1) Configurable sstl I/O set to 1.8v: Termination resistance: 344, 393, 458, 500, 550, 611, 688

Ohms and open

2) Configurable sstl I/O set to 1.5v: Termination resistance: 344, 393, 458, 500, 550, 611, 688

Ohms and open

Technology: TSMC 0.040um LP process.

[Disclaimer] This information is for modeling purposes only and is not guaranteed.

[Copyright] Copyright(c) Synopsys, Inc. 2010. All Rights Reserved.

Информация о компоненте и выводах

В Таблице 5.2 приведена расшифровка основных полей этой части IBIS-модели.

Таблица 5.2

| Ключевое слово | Обязательно ли наличие этой строки в файле (да/нет) | Описание |

|---|---|---|

| [Component] | да | Имя моделируемого компонента. Стандартной практикой является использование названия производителя. |

| [Manufacturer] | да | Название компан�ии-производителя. |

| [Package] | да | Параметры сопротивления, инддуктивности и ёмкости корпуса. |

| [Pin] | да | Информация о соответствии выводов и буферов. |

| [Package Model] | нет | Если модель использует сторонюю модель корпуса, то эта строка содержит имя модели корпуса. |

| [Pin Mapping] | нет | Информация о соединении буферов с землей и питанием. |

| [Diff Pin] | нет | Информация о буферах, ассоциированных с дифференциальными сигналами. |

| [Model Selector] | Выбор одного из нескольких, доступных на том же выводе, буферов для моделирования. |

Ниже частично приведена вторая часть IBIS-файла микросхемы 1892ВМ14Я.

|************************************************************************

| Component mcom02

|************************************************************************

|

[Component] mcom02

[Manufacturer] Manufacturer name

[Package]

| variable typ min max

R_pkg 0.51802 4.7421e-3 0.95421

L_pkg 4.774e-9 9.6e-11 9.857e-9

C_pkg 1.64e-12 9.598e-13 1.037e-11

|

[Package Model] ibis_a19424_a_101314

|

[Pin] Signal_name model_name R_pin L_pin C_pin

|

H35 CSI_VDD POWER

H36 CSI_VDD POWER

J35 CSI_VDD POWER

…..

|

|***********************PIN MAPPING*****************************************

|

[Pin Mapping] pulldown_ref pullup_ref gnd_clamp_ref power_clamp_ref ext_ref

|

H35 NC CSI_VDD

H36 NC CSI_VDD

…

|

|**********************DIFF PIN*********************************************

[Diff_pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

|lvds1

C27 D27 1.2V NA NA NA

C26 D26 1.2V NA NA NA

A24 B24 1.2V NA NA NA

A25 B25 1.2V NA NA NA

|lvds2

C24 D24 1.2V NA NA NA

C25 D25 1.2V NA NA NA

A27 B27 1.2V NA NA NA

A26 B26 1.2V NA NA NA

|ddr1

AD36 AD35 0.350V NA NA NA

T35 T36 0.350V NA NA NA

T33 T34 0.350V NA NA NA

AM35 AM36 0.350V NA NA NA

AM33 AM34 0.350V NA NA NA

|ddr2

AT23 AR23 0.350V NA NA NA

AR31 AT31 0.350V NA NA NA

AN31 AP31 0.350V NA NA NA

AR15 AT15 0.350V NA NA NA

AN15 AP15 0.350V NA NA NA

|usb

AT12 AR12 0.150V NA NA NA

|mipi dphy (csi)

G35 G36 0.200V NA NA NA

C36 C35 0.200V NA NA NA

D36 D35 0.200V NA NA NA

E36 E35 0.200V NA NA NA

F36 F35 0.200V NA NA NA

|mipi dphy (dsi)

G33 G34 0.200V NA NA NA

C34 C33 0.200V NA NA NA

D34 D33 0.200V NA NA NA

E34 E33 0.200V NA NA NA

F34 F33 0.200V NA NA NA

|

|***************************************************************************

| Model Selector

|***************************************************************************

|

[Model Selector] PDDRIO_PAD

MSD_D3RP2_18 DDR2 MSD_D3R_PDDRIO Z0=18-Ohm

MSD_D3RP2_40 DDR2 MSD_D3R_PDDRIO Z0=40-Ohm

MSD_D3RP2_48 DDR2 MSD_D3R_PDDRIO Z0=48-Ohm

MSD_D3RP2_ODT150 DDR2 MSD_D3R_PDDRIO cell 150-Ohm ODT Receiver

MSD_D3RP2_ODT50 DDR2

Информация для моделирования

В Таблица 5.3 представлен основной набор параметров и ключевых слов, определяющих характеристики модели.

Таблица 5.3

| Ключевое слово | Описание |

|---|---|

| [Model Spec] | Общий набор параметров для симуляции. |

| [Receiver Thresholds] | Пороговые значения для различных случаев симуляции. |

| [Temperature Range] | Температурный диапазон. |

| [Voltage Range] | |

| [Pulldown], [Pullup], [GND_clamp], [POWER_clamp] | |

| [Ramp], [Rising Waveform], [Falling Waveform] | |

| [Test Data], [Rising Waveform Near], [Rising Waveform Far], [Falling Waveform Near],[Falling Waveform Far], [Test Load] |

Перечень принятых сокращений

- BGA - Ball grid array package

- CSI - MIPI camera serial interface

- DDR - Dual data rate DRAM

- DSI MIPI - display serial interface

- EMC - Electromagnetic compatibility

- GPIO - General Purpose Input/Output pin that can be configured to be either an input output

- IBIS - Input output buffer information specification

- I2C - Inter-integrated circuit interface

- JTAG - Joint Test Action Group

- OTG - On-the-go

- PCB - Printed circuit board

- UART - Universal asynchronous receiver/transmitter

- USB - Universal Serial Bus

- VPI - Video processing units

- РП - Руководство пользователя

История изменений

- 11.07.2018 г.

- Удалена привязка документа к номерам партий микросхем.

- 05.08.2019 г.

- Скорректирована таблица 2.15.

- 24.10.2019 г.

- Добавлены рекомендации по подключению SD-карты.

- Добавлена рекомендация подключения подтягивающих резисторов к линиям SD0_DET, SD1_DET.

- 15.05.2020 г.

- Добавлен раздел «Рекомендации по подключению SPI-флеш»..

- Скорректирована таблица 2.15.

- 04.05.2023 г.

- Изменились рекомендации по подключению неиспользуемых интерфейсов (раздел 2.15, таблица 2.15), подключение выводов модуля EMAC.

- 25.03.2025 г.

- Скорректированы рекомендации по подключению выводов XTI_32K и XTO_32K при неиспользовании кварцевого резонатора 32,768 кГц.

- 06.05.2025 г.

- Документ импортирован из PDF редакции от 25.03.25 г.

- Изменены названия выводов на SDMMC0_18EN и SDMMC1_18EN во главе "Рекомендации по подключению Питания SD карты".

- Исправлены названия рисунков (рис.2.3 и рис.2.4) во главе USB.

- Обозначения физических величин приведены к стандарту.

- 29.10.2025 г.

- Скорректированы таблицы 2.3, 2.4, 2.15, 3.3.