Рекомендации по проектированию аппаратуры

В данном документе отражены некоторые нюансы, которые желательно учитывать при разработке принципиальной электрической схемы устройства на базе процессоров серии «Мультикор».

Подача питающих напряжений на процессор и старт процессора

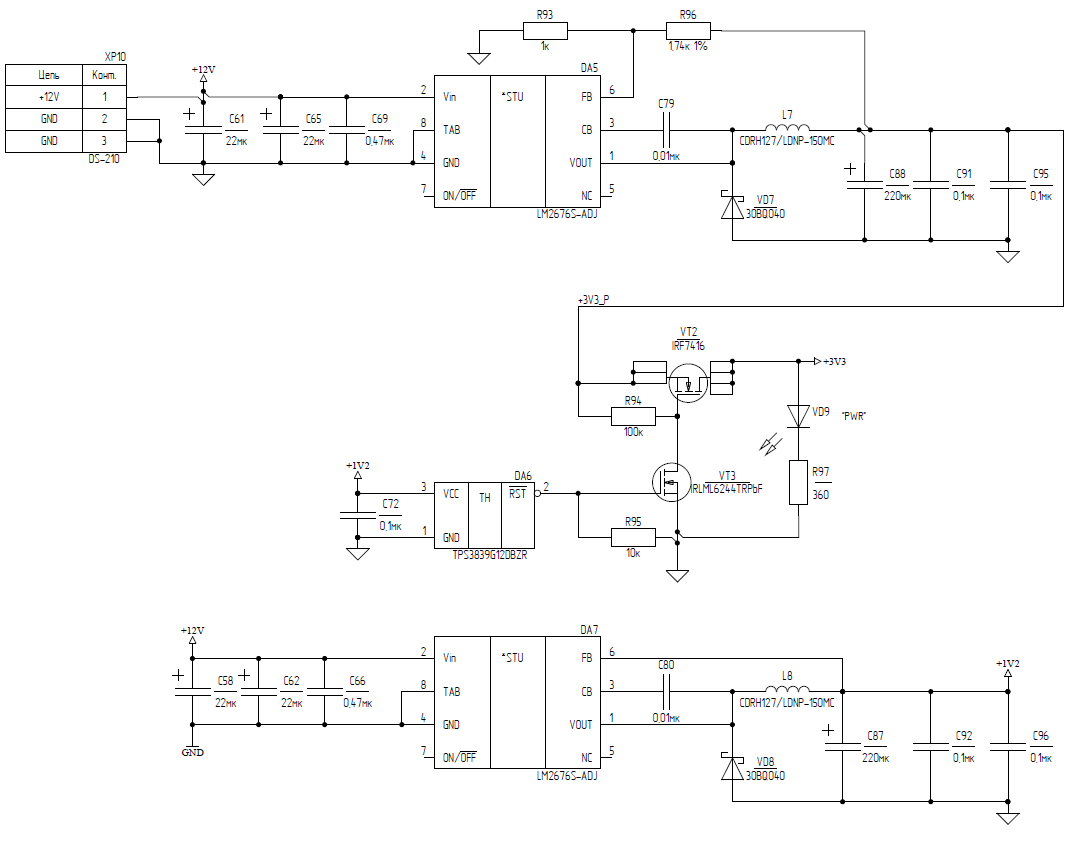

В руководстве пользователя и технических условиях на процессоры серии «Мультикор» обозначено требование подавать напряжение питания ядра (CVDD) не позднее напряжения питания периферии (PVDD). В качестве примера реализации такого условия может быть использован отладочный модуль NVCom-02TEM-3U. Часть его принципиальной электрической схемы приведена ниже. Приводимые в дальнейшем выдержки схем также взяты из схемы данного модуля, если не оговорено иное. Полностью схема отладочного модуля доступна на сайте.

Уровень напряжения 1.2 В (цепь +1V2, CVDD для процессора 1892ВМ10Я) подается на процессор напрямую, а подача напряжения 3.3 В (цепь +3V3, PVDD) управляется супервизором DA6, который не выдаст управляющий сигнал раньше, чем уровень напряжения CVDD достигнет минимально допустимого значения. Нарушение требуемого порядка подачи питающих напряжений не приводит к нестабильному поведению процессора или его немедленному выходу из строя. Однако данное требование необходимо соблюдать для обеспечения гарантированной наработки на отказ.

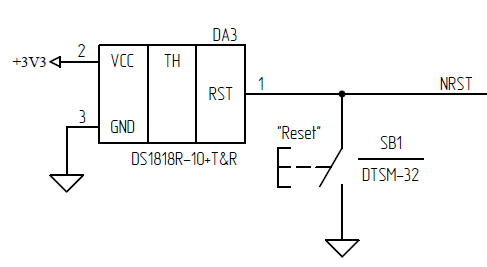

При старте процессора необходимо обеспечить кратковременный нулевой уровень на входах nRST и TRST процессора. В случае со входом nRST наиболее удобным способом представляется использование супервизора:

Дополнительно, до подачи всех питаний (CVDD, PVDD) и частоты XTI необходимо обеспечить PLL_EN = 0, п осле чего подать на него 1. Это необходимо для стабильного запуска микросхемы.

TRST - ресет блока oncd

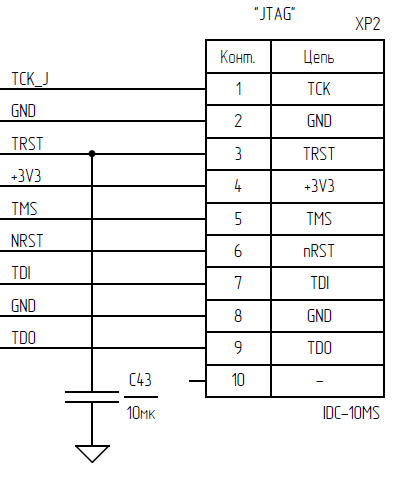

Вывод TRST — один из выводов интерфейса JTAG, обеспечивающего отладку с помощью блока OnCD в составе процессора. TRST — это ресет блока OnCD. Для работы по JTAG надо обеспечить его состояние в логической «1».

Для обеспечения кратковременного низкого уровня на нем при подаче питания на устройство проверенным решением является подключение его к «земле» через конденсатор емкостью 10 мкФ. Остальные выводы JTAG не требуют дополнительной обвязки на устройстве и могут быть выведены на разъем напрямую, см. рисунок ниже:

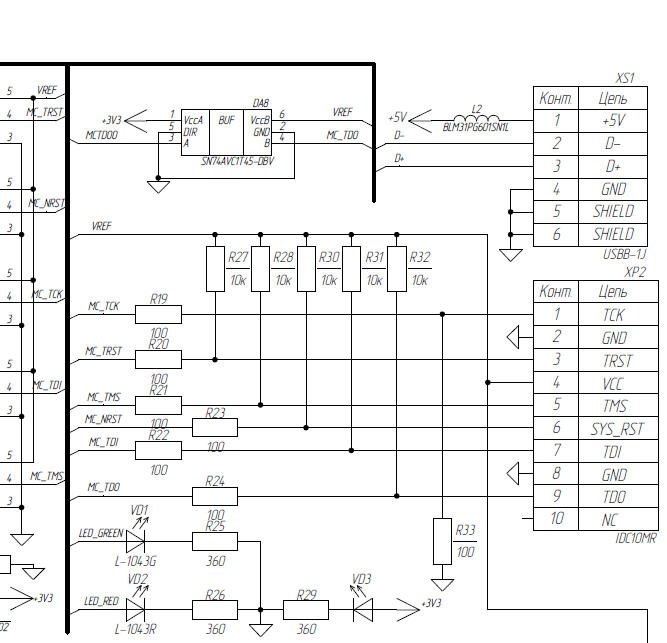

Реализация выходного каскада сигнала trst в usb-jtag

В качестве иллюстрации выходного каскада сигнала TRST в USB-JTAG представлена выдержка из схемы электрической USB-JTAG эмулятора, см. Рисунок 4.

Подключение памяти типа sdram

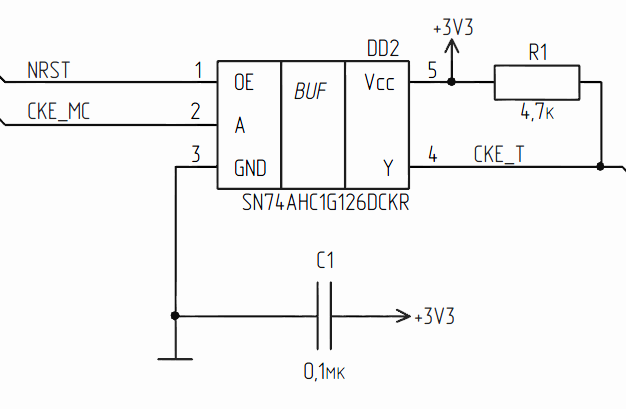

Порт внешней памяти процессоров серии «Мультикор» имеет в своем составе контроллер SDRAM, поэтому подключение динамического ОЗУ не требует дополнительных схемотехнических решений. Единственным исключением являются процессоры 1892ВМ7Я, 1892ВМ8Я, 1892ВМ10Я, имеющие особенность в реализации управления CKE. Особенность заключается в том, что при подаче сигнала nRST сигнал CKE сразу же переходит в состояние «активный ноль». Поэтому если сигнал nRST подается в момент чтения из SDRAM, микросхема памяти не завершит свой цикл работы и оставит выходы шины данных в активном состоянии. Это приведет к тому, что процессор не сможет после снятия nRST стартовать из загрузочной флеш-памяти, так как на линиях шины данных будут непредсказуемые значения. Этим обусловлено приведенное в руководстве пользователя требование завершить все операции с SDRAM перед подачей сигнала nRST.Проверенным решением в данном случае является подключение вывода CKE к микросхемам памяти SDRAM через буфер:

Цепь CKE_MC — это линия, идущая от вывода CKE процессора. Цепь CKE_T - линия, идущая ко входам CKE динамической памяти. Пока на вход nRST подается неактивный уровень (3.3 В) — сигнал CKE на микросхемы памяти приходит напрямую с процессора. Когда подается активный уровень — выход буфера переходит в третье состояние, и уровень на входе CKE памяти остается высоким за счет pull-up-резистора.

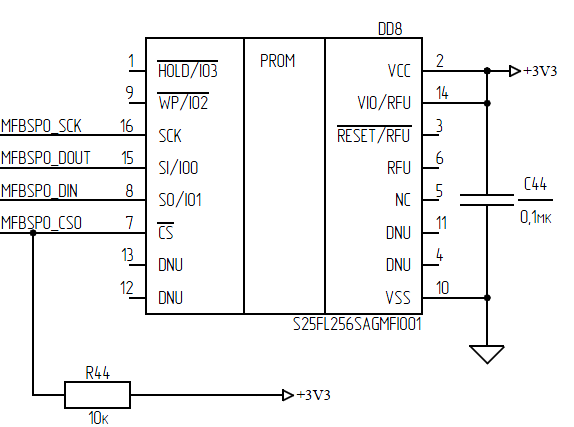

Подключение загрузочной SPI-флеш

При подключении загрузочной флеш-памяти с интерфейсом SPI необходимо учитывать, что в режиме загрузки из SPI процессор переводит в активное состояние оба выхода SS[1:0] порта MFBSP0. Поэтому второе SPI-устройство допустимо подключать к порту MFBSP0 только при условии, что во время загрузки отключается подача на него сигнала SS.

Кроме того, вход SS микросхемы SPI-флеш рекомендуется подтягивать к единице. Это требование приведено, как прав�ило, в описании микросхемы SPI-флеш. В противном случае не гарантируется стабильность работы микросхемы SPI-флеш после снятия сигнала nRST.

Подключение каналов spacewire

Каналы SpaceWire, согласно стандарту, на физическом уровне соответствуют стандарту LVDS. В процессорах серии «Мультикор» (а также в интерфейсных микросхемах SpaceWire) приемопередатчики LVDS для каналов SpaceWire реализованы в составе микросхемы. Таким образом, выводы SpaceWire микросхем необходимо подключать напрямую к разъемам на плате.

В составе приемников LVDS уже предусмотрены резисторы номиналом 100 Ом между сигналами SINN-SINP и DINN-DINP. Установка внешних резисторов между линиями приемников не требуется. На некоторых отладочных модулях также могут быть установлены внешние резисторы 100 Ом между линиями SINN-SINP, DINN-DINP. Это — рудимент, оставшийся от микросхем самых первых партий, которые не имели данных резисторов на кристалле. Данные микросхемы выпускались только в качестве опытных образцов и не поставлялись.Желательно предусмотреть в устройстве установку fail-safe резисторов согласно руководству пользователя на конкретный процессор серии «Мультикор».

Гальваническая развязка каналов spacewire

Стандарт SpaceWire не предполагает гальванической развязки. Поэтому, так или иначе, кабели SpaceWire должны содержать общий сигнал «земли». Если обратить внимание на кабель SpaceWire, описанный в стандарте, видно, что общая «земля» двух устройств, соединенных по SpaceWire, соединяет корпуса разъемов через внешнюю экранирующую оплетку кабеля. Фактически, это значит, что для работы кабеля, соответст вующего стандарту, необходимо соединять корпус разъема на плате с «землей» этой платы. В частности,такое решение использовано и в устройстве USB Brick фирмы StarDundee.

В отладочных модулях и другой аппаратуре АО НПЦ «ЭЛВИС» для работы по SpaceWire используется альтернативный вариант. Используемый кабель для обмена по SpaceWire — обычная витая пара. Контакты №3 разъемов SpaceWire двух устройств соединены посредством экранирующей оплетки кабеля. Опыт работы показывает, что использование такого кабеля обеспечивает корректную работу микросхем АО НПЦ «ЭЛВИС» на скоростях передачи данных, гарантированных документацией.

Подключение сигнальных выводов

Неиспользуемые входы процессора необходимо подтянуть к неактивному уровню. Неиспользуемые выходы подключать куда-либо не требуется. Также существуют нюансы подключения различных сигнальных выводов, которые рассмотрены ниже.

Сигнал немаскируемого прерывания (nmi)

Немаскируемое прерывание может генерироваться по фронту сигнала на входе NMI процессора «Мультикор». Не рекомендуется подключение или подтяжка резистором сигнала NMI к единице — в этом случае при подаче питания и снятии сигнала nRST процессор сгенерирует немаскируемое прерывание. Вне зависимости от того, планируется ли использовать данный сигнал в разрабатываемой аппаратуре, рекомендуется притягивать его к нулю.

Подключение питания неиспользуемых блоков

В Таблице 1 для каждой микросхемы серии «Мультикор» приведен список блоков и их выводов, допускающих неподачу питания.

Таблица 1. Перечень блоков с отдельным питанием

| Название микросхемы | Название блока | Название выводов питания | Примечание |

|---|---|---|---|

| 1892ВМ7Я | Приемники типа SSTL портов DDR_PORT0, DDR_PORT1 | VREF0,VREF1 | Допускает неподачу питания, если не используется DDR |

| 1892ВМ7Я | Приемопередатчики SSTL порта DDR_PORT0, DDR_PORT1 | DDR_PVDD0,DDR_PVDD1 | Допускает неподачу питания, если не используется DDR |

| 1892ВМ7Я | Контроллер SRIO | SR0_СVDD_TX SR0_PVDD_TX SR0_СVDD_RX SR0_PVDD_RX SR1_СVDD_TX SR1_PVDD_TX SR1_СVDD_RX SR1_PVDD_RX | Допускает неподачу питания, если не используется DDR |

| 1892ВМ12АТ | Приемники и передатчики контроллера GSWIC | GSW_TXVDD, GSW_RXVDD | Допускает неподачу питания, если не используется контроллер GSWIC |

| 1892ВМ15АФ | Приемопередатчики GigaSpaceWire контроллера SPFMIC | gSW_VDD_0 – gSW_VDD_3. gSW_TXVDD_0 – gSW_TXVDD_3.gSW_RXVDD_0 – gSW_RXVDD_3. | Допускает неподачу питания, если не используется контроллер SPFMIC |

| 1892ВМ15АФ | Приемопередатчики SpaceFibre контроллера SPFMIC | SpF_VDD_0 – SpF_VDD_1. SpF_TXVDD_0 – SpF_TXVDD_1. SpF_RXVDD_0 – SpF_RXVDD_1 | Допускает неподачу питания, если не используется контроллер SPFMIC |

| 1892ВМ15АФ | Приемники типа SSTL портов DDR_PORT0, DDR_PORT1 | VREF0, VREF1 | Допускает неподачу питания, если не используется DDR |

| 1892ВМ15АФ | Приемопередатчики SSTL порта DDR_PORT0, DDR_PORT1 | DDR_PVDD0,DDR_PVDD1 | Допускает неподачу питания, если не используется DDR |

| 1892ВМ206 | Приемопередатчики SpaceFibre контроллера SPFMIC | SpF_VDD_0 – SpF_VDD_1 SpF_TXVDD_0 – SpF_TXVDD_1 SpF_RXVDD_0 – SpF_RXVDD_1 | Допускает неподачу питания, если не используется контроллер SPFMIC |